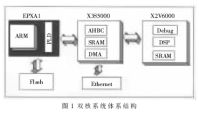

介紹了以ARM+DSP體系結構為基礎的FPGA實現。在其上驗證應用算法,實現了由ARM負責對整個程序的控制,由DSP負責對整個程序的計算,最大程度地同時發揮了ARM和DSP的各自優勢。

ARM通用CPU及其開發平臺,是近年來較為流行的開發平臺之一,而由ARM+DSP的雙核體系結構,更有其獨特的功能特點:由ARM完成整個體系的控制和流程操作,由DSP完成具體的算法和計算處理。這樣,不但可以充分地發揮ARM方便的控制優勢,同時又能最大限度地發揮DSP的計算功能。這在業界已逐漸成為一種趨勢。

本

關鍵字:

ARM DSP FPGA 軟硬件協同驗證 SoC

系統級芯片(SoC)中存儲器容量的增加以及嵌入式存儲器支配整個裸片良品率的事實,使良品率設計(DFY)面臨日...

關鍵字:

SoC 存儲 代碼 結構 邏輯 密度 單元 密度

血壓是人體重要的生理參數之一,對其進行精確測量,有利于早期發現和鑒別高血壓類型,提出合理的治療建議。目前,臨床上對普通病人主要采用無創檢測的方法,它大致分為人工柯氏音法和示波法兩類。人工柯氏音法雖然比較準確,但操作困難,受主觀因素影響較大;傳統的示波法雖然操作簡單,但穩定性和個體適應性較差,不利于在臨床應用上的普及和推廣。本文在示波法的基礎上,從硬件實現和軟件設計兩個方面改進了原來的測量方法,并進行了比對測試。

1 硬件設計

示波法進行血壓檢測的主要過程是獲取袖帶內變化的壓力信號,分析從中

關鍵字:

SoC 電子血壓檢測儀 示波法 形態濾波 人工柯氏音法

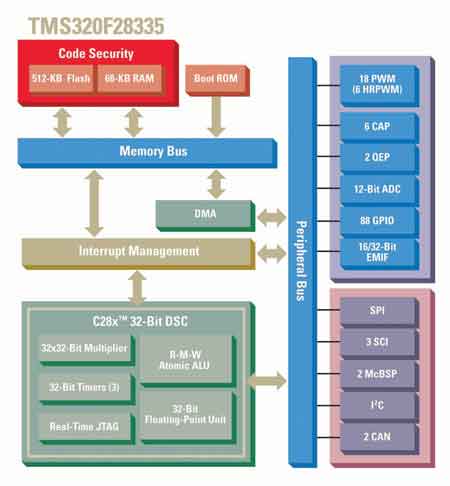

DSC(Digital signal controller,數字信號控制器)是一種面向高端嵌入式系統的最先進的單片控制處理器。基于浮點架構的DSC具有更快的處理速度,所需的程序儲存容量更少,支持更高級的有助于節省功耗的計算算法,同時進一步擴展了系統的性能。浮點編程比定點編程的速度更快,SoC(system-on-a-chip,片上系統)的集成方式能夠有效控制板級空間、元件數量和整體系統開銷。

隨著嵌入式系統承擔的任務越來越復雜,不論是降低功耗還是實現諸如汽車導航之類的新功能,它們都需要具有更高性

關鍵字:

DSC 數字信號控制器 浮點 SoC 控制系統

Analog Devices推出的兩款針對電能市場中日益復雜的通信網絡要求而設計的ADE51xx和ADE55xx單芯片計量器件,擴展了其領先市場的電能計量產品系列。全球來看,固態電子式電能表正逐步替代故障率高、容易竊電且不易于支持諸如遠程抄表和分時計費等新功能的機電式電能表。而這些新功能的實現以及對計量網絡更高的可靠性要求使得其需要更大的存儲器容量,以滿足電能行業日益增長的數據量要求。ADI公司的新款SoC(片上系統)電能計量IC集成了62 KB的片內閃存和2 KB的RAM(隨機存取存儲器),與其它同

關鍵字:

SoC ADI 計量 電能 存儲器

為數字消費、家庭網絡、無線、通信和商業應用提供業界標準架構、處理器及模擬 IP 的領先廠商 MIPS 科技公司(MIPS Technologies Inc.,納斯達克交易代碼:MIPS)今天宣布,BroadLight已經選擇高性能 MIPS32® 24K® 內核作為其新型 GPON 系統級芯片(SoC)的基礎核心。BroadLight 今天還宣布針對光纖到戶(fiber-to-the-home,FTTH)應用的 BL2348 GPON 家庭網關(RG)SoC 解決方案已經開始提供樣品。

關鍵字:

BroadLight SoC MIPS 集成電路 GPON

引 言

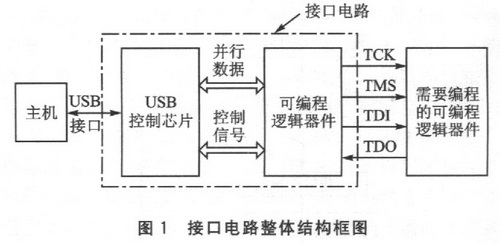

隨著片上系統(SoC,System on Chip)時代的到來,包括復雜可編程邏輯器件(CPLD,Complex ProgrammableLogic Devi(e)和現場可編程門陣列(FPGA,Field Programmable Gate Array)的可編程邏輯器件(具有在系統可再編程的獨特優點),應用越來越廣泛。這給用于可編程邏輯器件編程的下載電纜提出了更高的要求。

本文研究基于IEEEll49.1標準的USB下載接口電路的設計及實現。針對Altera公司的FPGA器件Cy-

關鍵字:

CPLD USB FPGA 下載電纜 SoC

引 言

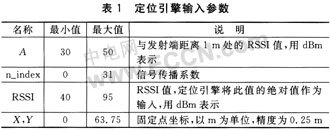

CC2431是TI公司推出的帶硬件定位引擎的片上系統(SoC)解決方案,能滿足低功耗ZigBee/IEEE 802.15.4無線傳感器網絡的應用需要。CC2431定位引擎基于RS-SI(Received Signal Strength Indicator,接收信號強度指示)技術,根據接收信號強度與已知參考節點位置準確計算出有關節點位置,然后將位置信息發送給接收端。相比于集中型定位系統,RSSI功能降低了網絡流量與通信延遲,在典型應用中可實現3~5 m定位精度和0.25 m的分辨率。本文在

關鍵字:

SoC RSSI 定位 寄存器 TI

在SoC系統設計方面,現在還有一些人們幾乎未涉足的領域,而這些領域將對降低功耗產生最大的推動作用。幸運的是,人們現在已經擁有大量針對這一領域的設計工具。在近日美國舊金山舉辦的Electronic Summit2008上,Mentor Graphics的ESL-HDL部門總經理Glenn Perry介紹了系統級設計需要考慮的方方面面。

系統架構方面的改進將帶來巨大的好處,不過在EDA世界,人們只有在設計的較晚階段才使用功耗仿真工具,如門級和物理實現級。那為何不在系統級進行這些工作?原因主要包括:

關鍵字:

SoC 功耗 EDA

系統級設備往往是能耗的最終反映。在考慮功耗降低時,往往需要從四個層次來考慮。在近日舊金山舉行的Electronic Summit2008上,Cadence公司低功耗市場行銷總監Mohit Bhatnagar舉例了數據中心設備的低功耗考慮。

第一是服務器中心,即綠色電網的問題,如果你采用相同的IC、工藝、軟件,你能讓設計出的數據中心的功耗更低嗎?數據分析表明,考察一個數據中心時,45%的功耗出現在服務器元件上,諸如存儲器或CPU;另外的45%則是用于冷卻它們。因此,其中90%的功耗是半導體集成電路

關鍵字:

功耗 CPU SoC

1、便攜式設備對處理器提出的挑戰

隨著電子便攜式設備在全球的風行,人們對電子便攜式設備的要求也越來越高,希望產品有更多的功能,如手機攝像機自動對焦與手機閃信與計步器;希望產品功耗更低,如無線設備、手持POS機和家庭醫療產品;希望產品體積更小,如運動手表;希望產品的保密性好;處理能力強,如便攜式儀器和高精度運動控制;希望價格更低和開發周期短。

然而困惑的是,很多的便攜式設備往往會同時要有上面的多個要求,然而現實中很難做到:同時滿足高速處理、低功耗和價格?ARM高速,但是功耗而

關鍵字:

SoC ARM MCU

如果你打算設計一個包含數字音頻的SoC系統,或者正在進行這樣一個項目,那么花幾分鐘時間閱讀本文可以幫助你在各種技術參數之間做出更好的平衡,避免設計方向出現偏差,提高流片的成功率,從而節省數周的開發時間。我們將為你逐一分析設計備選方案,評估中的關鍵因素以及由此做出的決策。

消費類音頻產品的歷史

消費類音頻產品的歷史最早可以追溯到130年前,在開始的100年間,音頻回放只能采用模擬技術。那時采用數字技術的產品體積龐大,價格昂貴,對于消費類產品來說也過于復雜。直到1982年,CD光盤和CD播放器的

關鍵字:

SoC 數字音頻 CD光盤 MP3

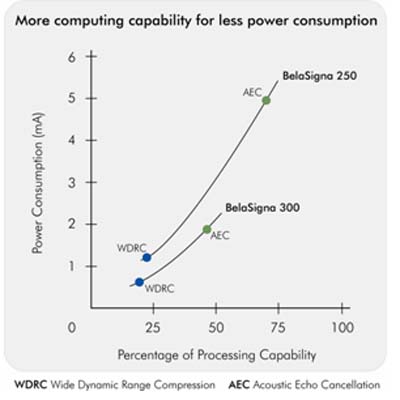

當前,降低功耗不僅成為節電的必由之路,并且被賦予了環保的神圣使命。因此所有的設計者都十分關心功耗問題。不過,在設計時還要謹防過度設計(overdesign)現象,使各個部分協調一致,達到整個功耗的降低。

應用是個很復雜的問題,其中有許多要素。你需要針對問題提供整體化的解決方案。在深刻理解最終應用的情況下,你會發現是否出現了過度設計;有時候,出于市場等方面的考慮,會出現過度設計的做法,這最終會導致功耗過高。

系統設計與SoC設計的相對比例問題,軟、硬件比例問題,IC的驅動電壓是否越低就越好?

關鍵字:

降低功耗 SoC 過度設計 DSP Bolosigno 300 Bolosigno250

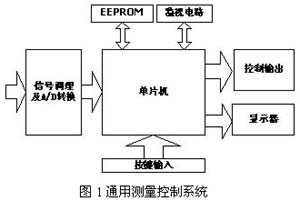

1 引言

智能測量控制電路系統在工業控制、各種消費類電子產品獲得了廣泛的應用。它一般是以單片機為核心,外加模擬信號調理、模數轉換、人機接口(包括按鍵和數碼顯示等)、功率輸出等幾部分組成,其系統框圖如圖1。測控系統是基于PCB板來設計的,體積和功耗都較大。特別是為了使系統能夠應用在各種惡劣的工作環境下,設計者通常要化大量的時間和精力來研究和實施各種硬件和軟件的抗干擾措施。另外,這些系統都具有大多數的共性,設計師很多的工作都是重復的。

2 系統結構

隨著集成電路的設計技術和深亞微米制造技

關鍵字:

智能測量 PCB板 SoC

1 引 言

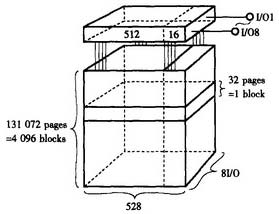

Flash因為具有非易失性及可擦除性在數碼相機、手機、個人數字助理( PDA)、掌上電腦、MP3播放器等手持設備中得到廣泛的應用。自1989年東芝公司發表了Nand Flash結構以來, Nand Flash以其相對于Nor Flash具有更小的體積,更快的寫入和擦除速度,更多次的可擦除次數,以及更低廉的每bit價格得到了迅速發展。大容量的Nand Flash特別適合現在數碼設備中大數據量的存儲攜帶,可以降低成本,提高性能。

ARM7TDMI是世界上廣泛使用的32位嵌入式RIS

關鍵字:

Flash ARM SoC

soc介紹

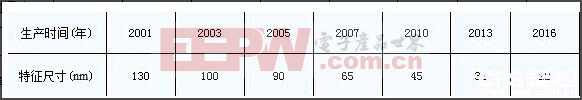

SoC技術的發展

集成電路的發展已有40 年的歷史,它一直遵循摩爾所指示的規律推進,現已進入深亞微米階段。由于信息市場的需求和微電子自身的發展,引發了以微細加工(集成電路特征尺寸不斷縮小)為主要特征的多種工藝集成技術和面向應用的系統級芯片的發展。隨著半導體產業進入超深亞微米乃至納米加工時代,在單一集成電路芯片上就可以實現一個復雜的電子系統,諸如手機芯片、數字電視芯片、DVD 芯片等。在未 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473