德國慕尼黑,2022年12月7日——處理器設計自動化和RISC-V處理器IP的領導者Codasip今日宣布成立Codasip實驗室(Codasip Labs)。作為公司內部創新中心,新的Codasip實驗室將支持關鍵應用領域中創新技術的開發和商業應用,覆蓋了安全、功能安全(FuSa)和人工智能/機器學習(AI/ML)等方向。該實驗室的使命在于識別和構建相關技術,以擴展定制計算的可能性,并加快具有定制化的、領域專用設計的差異化產品的開發,并縮短其上市時間。Codasip實驗室將由公司創始人兼總裁馬克仁(Ka

關鍵字:

Codasip Codasip 實驗室 IP RISC-V

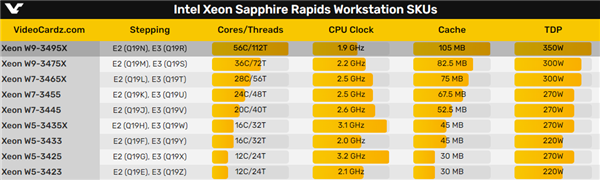

還記得2018年Intel推出的至強W-3175X處理器嗎?當年這是Intel為了跟AMD競爭專業市場,將服務器版至強下放到了工作站,滿血28核56線程,還是唯一解鎖超頻的至強,售價超過2萬元。這款處理器在2021年就退役了,這兩年Intel的發燒級HEDT平臺也沒了動靜,至強W的繼任者也沒了音信,一度傳聞被取消,但是Intlel現在親自出面,證實了新一代工作站處理器要來了。他們的官推來看,Intel稱新一代的工作站處理器非常快,暗示性能強大,甚至需要用戶重新規劃下去接咖啡的時間了,因為工作等待時間會更短

關鍵字:

英特爾 CPU 至強 DDR5

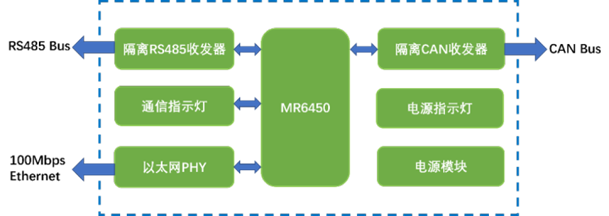

隨著AIoT時代的到來,RISC-V作為新興架構,其精簡及開源的特性在物聯網的應用領域有很大的優勢,為此ZLG致遠電子推出MR6450系列RISC-V核心板,下面詳細為大家介紹其具體參數與典型應用。MR6450核心板性能如何?MR6450系列核心板基于先楫半導體的HPM6450IVM1開發,主頻高,支持高速數據處理能力,具有豐富的通信接口,適合于工業控制、儀器儀表、電機控制等應用場合。核心特點:● 單核32位 RISC-V 處理器,816MHz主頻,高于9000 CoreMark?和4500以上的DMIP

關鍵字:

MR6450 RISC-V核心板

據Intel最新對外公布的信息,Intel 4nm芯片已準備投產,將用于包括Meteor Lake(14代酷睿流星湖)處理器、ASIC網絡產品等。同時,Intel 3nm、20A(2nm,其中A代表埃米,1nm=10埃米,下同)、18A(1.8nm)進展一切順利,甚至還略有提前。其中Intel 3nm將在明年下半年投產,用于Granite Rapids和Sierra Forest數據中心產品。Intel 20A計劃2024上半年準備投產,首發Arrow Lake(15代酷睿)客戶端處理器,18A提前到20

關鍵字:

CPU Intel

11月29日,由港華集團名氣家主辦的“港華芯暨生態合作發布會”于蘇州港華大廈順利舉行。名氣家戰略合作伙伴賽昉科技、微五科技、芯昇科技、愛旗科技、紫光展銳、移遠通信、中國電信、中國移動的代表們通過線上線下共同參與。能源行業的數字化、智能化轉型正全面提速,與此同時信息安全體系建設和完善也被提到前所未有的高度。隨著國家出臺《關鍵信息基礎設施安全保護條例》,特別提出要重點保障包括能源行業在內的關鍵信息基礎設施的安全。港華集團作為城市燃氣基礎設施服務商率先行動,以“港華芯”為抓手,致力于在筑牢行業數據安全“防火墻”

關鍵字:

港華芯 安全芯片 RISC-V

中國上海——2022年11月23日——嵌入式開發軟件和服務的全球領導者 IAR Systems 與領先的端側 AI 芯片研發供應商嘉楠科技 (NASDAQ: CAN) 今天共同宣布,IAR Systems 最新推出的 Embedded Workbench for RISC-V 3.11.1版本已支持嘉楠勘智K510芯片,助力開發雙核RISC-V 64位 AI 端側推理芯片。IAR Embedded Workbench for RISC-V是一個完整的C/C++編譯器和調試器工具鏈,將嵌入式開發者所需的一切

關鍵字:

IAR Systems 嘉楠 RISC-V AI芯片

IT之家 11 月 22 日消息,榮耀 80 標準版發布前一天,高通官網公布了驍龍 782G(SM7325-AF)的參數。高通驍龍 782G 采用 6nm 工藝打造,是驍龍 778G+ 的繼任者,配備 8 核 CPU,包括 2.7GHz 的單核Cortex-A78 + 2.2GHz 的三核Cortex-A78 + 1.9GHz 的四核Cortex-A55,GPU 搭載Adreno 642L。高通稱,驍龍 782G 比驍龍 778G+ 的 CPU 提升了 5%,GPU 提升了 10%。其余外圍支持方面,驍龍

關鍵字:

高通 驍龍 782G芯片 CPU

瑞典烏普薩拉 - 2022 年 11 月 17 日 - 嵌入式開發軟件和服務的全球領導者 IAR Systems? 宣布其最新版本的 IAR Embedded Workbench for RISC-V 3.11版現已完全支持 Andes Technology(晶心科技)旗下 AndeStar? V5 RISC-V 處理器的 CoDense? 擴展。CoDense? 是處理器 ISA(指令集架構)的專利擴展,能夠幫助 IAR 的工具鏈生成緊湊的代碼,從而節省目標處理器上的閃存,而在之前版本中已實現支持的 A

關鍵字:

IAR Embedded Workbench for RISC-V Andes CoDense

德國慕尼黑市,2022年11月 - 處理器設計自動化和RISC-V處理器硅知識產權(IP)的領導者Codasip日前宣布,其已收購Cerberus Security Labs公司。Cerberus的物聯網(IoT)安全IP和經驗豐富的團隊將支持Codasip的客戶能夠快速為RISC-V處理器設計集成安全解決方案。此項收購未披露具體金額,且收購事項已完成并立即生效。總部位于英國布里斯托爾的Cerberus團隊將作為Codasip員工加入到團隊。Codasip首席執行官Ron Black評論道:“安全性是互聯

關鍵字:

Codasip Cerberus RISC-V處理器

圖源:東方IC芯片行業兩家重量級企業Arm和高通的法庭訴訟進入攻防戰階段,而近期傳出的相關消息,更有可能對全球芯片行業的發展帶來極大的影響。高通在近期提交給法庭的一份證據中提到,Arm在與其他客戶溝通時表示,高通所獲授權在2024年到期后不再續簽,這也意味著高通將不能再提供Arm架構的芯片。另外,所有獲得Arm授權的半導體制造商將無法向OEM客戶提供CPU外的其他SoC組件,包括GPU、NPU等,因為Arm計劃將CPU許可證協議與這些組件的許可證協議打包在一起授權。這場訴訟源于高通2021年收購了芯片設計

關鍵字:

RISC-V 龍芯中科 LoongArch架構

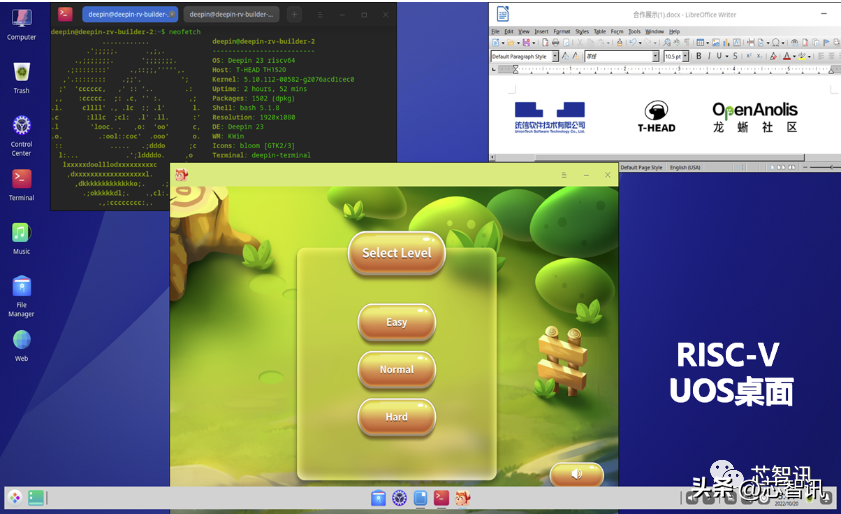

在“2019 阿里云峰會”上,阿里平頭哥正式發布了當時業界最強的高性能RISC-V處理器內核——玄鐵C910,引發了業界的廣泛關注。實際上,早在2014年之時,平頭哥副總裁孟建熠就已經開始關注RISC-V,2018年,平頭哥成功研發一款低功耗的RISC-V內核玄鐵E902。此后,平頭哥持續深耕RISC-V領域,并迅速成為了RISC-V領域的領導廠商。11月3日,在杭州舉行的“2022云棲大會”上,平頭哥發布全新的RISC-V高能效處理器——玄鐵C908。據介紹,玄鐵C908計算能效全球領先,較業界同性能處

關鍵字:

RISC-V 平頭哥 玄鐵C910

在萬物互聯的新時代,RISC-V架構憑借簡潔、模塊化、可擴展等特點迅速發展,并與X86、Arm漸成三足鼎立之勢。作為RISC-V生態重要參與者之一,阿里平頭哥在11月3日云棲大會上,發布全新RISC-V高能效處理器玄鐵C908,并在端側平頭哥引領RISC-V架構首次進入安卓開源生態體系,推動RISC-V與全球主流移動操作系統生態接軌。30多行業實現商業落地當前,RISC-V架構正朝著可擴展的模塊化、ISA(指令集)定制化以及軟硬件全棧優化的方向發展。平頭哥不斷擴寬RISC-V性能及應用邊界,今年發布無劍6

關鍵字:

RISC-V 智能穿戴 RTOS

北京時間 11 月 3 日晚間消息,據報道,高通 CEO 兼總裁克里斯蒂亞諾?阿蒙(Cristiano Amon)今日表示,2024 年將是 Windows PC 使用驍龍(Snapdragon)處理器大放異彩的一年。阿蒙在今日的財報電話會議上稱:“基于我們當前所積累的相關設計,采用驍龍處理器的 Windows PC 將在 2024 年出現拐點。”阿蒙所做的這一預測,主要基于微軟 Windows 系統的 AI 功能,越來越多的 PC 廠商采用驍龍處理器,以及進一步的設計工作使驍龍越來越適合于 Window

關鍵字:

高通 驍龍 CPU Windows PC

德國慕尼黑和韓國首爾,2022年11月——可定制RISC-V處理器知識產權(IP)的領導者Codasip日前宣布,SiliconArts已采用面向特定應用的Codasip 7系列RISC-V處理器,并使用Codasip Studio定制化工具。SiliconArts是為高端圖形處理提供創新解決方案的領導者,通過其極具真實感的光線追蹤圖形渲染技術實現沉浸式體驗。Codasip RISC-V處理器IP與SiliconArts光線追蹤圖形處理器(GPU)相結合,將為下一代要求最苛刻的增強現實應用賦能。Silic

關鍵字:

Codasip SiliconArts 光線追蹤GPU RISC-V

IT之家 11 月 3 日消息,SiFive 宣布推出兩款高性能 RISC-V 處理器,旨在為“下一代可穿戴設備和智能消費設備”提供動力,型號為 P670 和 P470。據介紹,SiFive P670 和 P470 支持虛擬化,包括用于加速虛擬化設備 I / O 的單獨 IOMMU,以及基于去年批準的 RISC-V Vector v1.0 規范的完整無序矢量實現,還號稱是市場上第一個支持新的 RISC-V 矢量加密擴展的芯片,最多支持 16 個內核的集群一起工作。S

關鍵字:

RISC-V 智能穿戴

risc-v cpu介紹

您好,目前還沒有人創建詞條risc-v cpu!

歡迎您創建該詞條,闡述對risc-v cpu的理解,并與今后在此搜索risc-v cpu的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473