一種基于DDS和PLL技術(shù)本振源的設(shè)計(jì)與實(shí)現(xiàn)

頻率合成技術(shù)作為現(xiàn)在電子系統(tǒng)中的一種關(guān)鍵技術(shù),已廣泛應(yīng)用于通信、雷達(dá)、電子對(duì)抗、定位導(dǎo)航、廣播電視、遙測(cè)遙控、儀器儀表等許多領(lǐng)域并得到了快速的發(fā)展,它是用一個(gè)或多個(gè)高穩(wěn)定、高精確度的標(biāo)準(zhǔn)頻率源作為參考,通過(guò)對(duì)頻率進(jìn)行加、減、乘、除等一系列變換,從而產(chǎn)生同樣高穩(wěn)定度和精確度的大量離散頻率的技術(shù)。頻率合成器的實(shí)現(xiàn)方式有4種:直接模擬頻率合成器(DAS)、鎖相環(huán)頻率合成器(PLL)、直接數(shù)字頻率合成器(DDS)和混合結(jié)構(gòu)(PLL+DDS)。其中,第1種已很少使用,第2~4種都有廣泛的使用。應(yīng)根據(jù)頻率合成器的使用場(chǎng)合、指標(biāo)要求確定具體使用哪種方案。

隨著電子技術(shù)的不斷發(fā)展,各類電子系統(tǒng)對(duì)頻率合成器的要求越來(lái)越高,對(duì)相位噪聲、頻率轉(zhuǎn)換時(shí)間、頻率分辨率、相對(duì)工作帶寬、體積及功耗等多種指標(biāo)也提出了更高的要求。在某項(xiàng)課題研究中,根據(jù)接收機(jī)的結(jié)構(gòu),接收機(jī)需要頻綜部分提供一個(gè)1 514 MHz(77 200 MHz/51△1 514 MHz)的下變頻本振信號(hào),為實(shí)現(xiàn)載波同步,需要快速地調(diào)整下變頻本振信號(hào)的頻率、相位,其頻率調(diào)整范圍不大,在10 MHz以內(nèi)。如果單獨(dú)選用鎖相環(huán)頻率合成器(PLL),則可實(shí)現(xiàn)結(jié)構(gòu)簡(jiǎn)單、體積小、易于集成、調(diào)試方便、雜散低等優(yōu)點(diǎn),但是頻率轉(zhuǎn)換時(shí)間相對(duì)較長(zhǎng),而直接數(shù)字頻率合成器(DDS)是一個(gè)全數(shù)字化的系統(tǒng),具有易于集成、極快的跳頻速度、極高的頻率分辨率和頻率切換時(shí)相位連續(xù)等優(yōu)點(diǎn),缺點(diǎn)就是雜散比較大、輸出頻率低。所以根據(jù)這兩種頻率合成器的特點(diǎn),本文采用DDS和PLL相結(jié)合,利用DDS作為參考信號(hào)源,以DDS激勵(lì)PLL的頻率合成方案。

1 系統(tǒng)原理

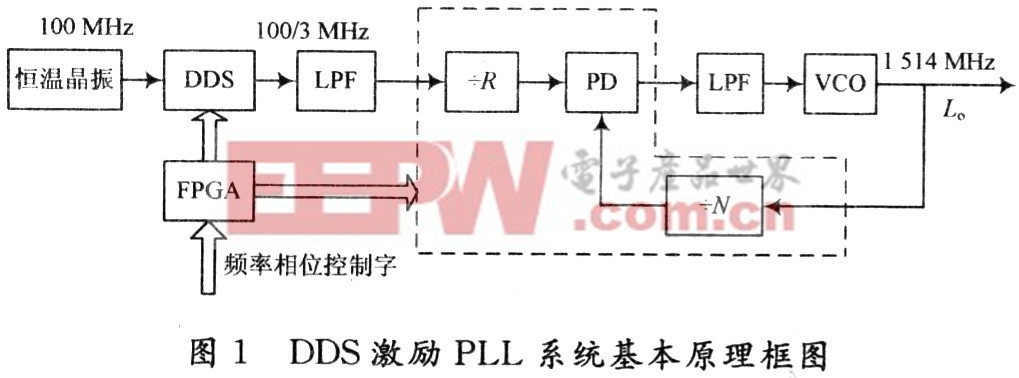

以DDS激勵(lì)PLL的基本原理組成框圖如圖1所示,采用高穩(wěn)定的石英晶體振蕩器作為DDS的參考時(shí)鐘源;通過(guò)FPGA把頻率控制字和相位控制字寫入DDS內(nèi)部的寄存器中,DDS便可以產(chǎn)生一個(gè)頻率和相位都可編程控制的模擬正弦波輸出;然后把DDS的輸出信號(hào)作為PLL的參考信號(hào);最后根據(jù)期望輸出的信號(hào)頻率,設(shè)定分頻器的分頻比N,便得到了頻率為DDS輸出頻率N/R倍的時(shí)鐘信號(hào)。

這種結(jié)構(gòu)利用DDS的高分辨率保證了足夠小的頻率步進(jìn),同時(shí)PLL的帶通特性很好地抑制了DDS輸出頻譜中的部分雜散。該方案實(shí)現(xiàn)了DDS和PLL的優(yōu)勢(shì)互補(bǔ),兼顧了各個(gè)方面的性能,所以此方案實(shí)現(xiàn)的本振源做到了比較高的頻率、較快的頻率轉(zhuǎn)換速度和較高的頻率分辨率,同時(shí)也很好地保證了系統(tǒng)雜散和相位噪聲性能。

2 電路設(shè)計(jì)

本設(shè)計(jì)系統(tǒng)的整個(gè)電路主要包括兩大部分,即DDS部分和PLL部分。

2.1 DDS部分

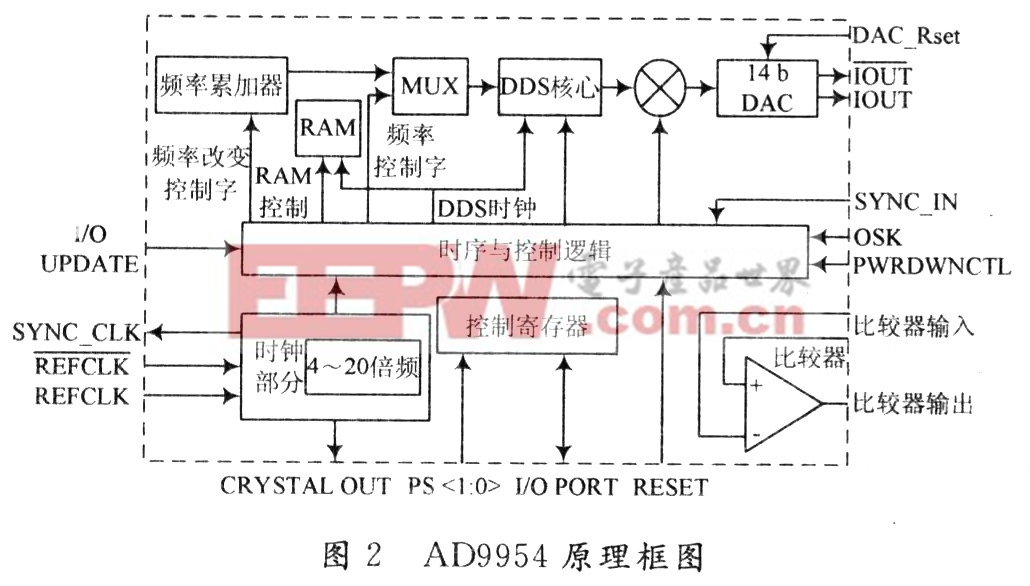

DDS部分的時(shí)鐘輸入選用100 MHz的恒溫晶體振蕩器;DDS部分的核心采用美國(guó)AD公司生產(chǎn)的大規(guī)模集成芯片AD9954,它是用先進(jìn)的DDS技術(shù)開(kāi)發(fā)的高集成度DDS器件,內(nèi)置高速、高性能D/A轉(zhuǎn)換器及超高速比較器,可作為數(shù)字編程控制的頻率合成器,能產(chǎn)生0~160 MHz的正弦波信號(hào)。AD9954內(nèi)含1 024×32 b靜態(tài)RAM,利用該RAM可實(shí)現(xiàn)高速調(diào)制,并支持幾種掃描模式。AD9954可提供自定義的線性掃描操作模式,通過(guò)AD9954的串行I/O口輸入控制字可實(shí)現(xiàn)快速變頻且具有良好的頻率分辨率。其應(yīng)用范圍包括靈敏頻率合成器、可編程時(shí)鐘發(fā)生器、雷達(dá)和掃描系統(tǒng)的FM調(diào)制源以及測(cè)試和測(cè)量裝置等,其內(nèi)部結(jié)構(gòu)如圖2所示。

DDS電路設(shè)計(jì)應(yīng)遵循的主要原則是使其輸出信號(hào)具有較好的控制時(shí)序、較低的相位噪聲和窄帶雜散,其次是正確的電路鋪設(shè)和連接,DDS的外圍電路并不復(fù)雜,主要由低壓差穩(wěn)壓電源NCP1117和低通濾波器SCLF-30等組成。AD9954頻率控制字為32位,在本應(yīng)用中系統(tǒng)工作時(shí)鐘為100 MHz,輸出時(shí)鐘的頻率分辨率△f1=100 MHz/232=0.023 Hz。AD9954相位控制字為14位,輸出時(shí)鐘的相位分辨率△φ1=360°/214=0.022。

2.2 PLL部分

PLL部分主要包括預(yù)分頻器、分頻器、鑒相器、環(huán)路濾波器和’VCO。根據(jù)設(shè)計(jì)需要采用鎖相環(huán)頻率合成器集成芯片ADF4112,它集成了預(yù)分頻器、分頻器、鑒相器等各種重要部件,如圖3所示。它由一個(gè)低噪聲數(shù)字鑒相器、一個(gè)高精度電荷泵、一個(gè)可編程參考分頻器(R分頻器)、一個(gè)可編程A,B計(jì)數(shù)器以及一個(gè)雙模分頻器P/P+1組成。6位A計(jì)數(shù)器、13位B計(jì)數(shù)器與雙模分頻器P/P+1共同組成了N分頻器,分頻比N=BP+A。數(shù)字鑒相器用來(lái)對(duì)R計(jì)數(shù)器和N計(jì)數(shù)器的輸出相位進(jìn)行比較,然后輸出一個(gè)與二者相位誤差成比例的誤差電壓。鑒相器內(nèi)部還有一個(gè)可編程延遲單元,用來(lái)控制翻轉(zhuǎn)脈沖的寬度,這個(gè)翻轉(zhuǎn)脈沖保證鑒相器的傳遞函數(shù)沒(méi)有死區(qū),因此降低了相位噪聲和參考雜散。該芯片的主要性能特點(diǎn)如下:

工作電壓:2.7~5.5 V,同時(shí)還提供外部可調(diào)的電荷泵電壓調(diào)節(jié)功能;最高鑒相頻率為55 MHz,最高RF輸入頻率達(dá)3 GHz;具有四組可編程雙模分頻器8/9,16/19,32/33,64/65;內(nèi)置可編程電荷泵電流和可編程反沖脈寬功能;編程控制采用3線串行接口;能夠進(jìn)行模擬和數(shù)字鎖定檢測(cè);軟、硬件斷電模式;具有良好的相位噪聲參數(shù)。

評(píng)論