- DDR3存儲器系統可以大大提升各種數據處理應用的性能。然而,和過去幾代(DDR和DDR2)器件相比,DDR3存儲器器件...

- 關鍵字:

FPGA IP核 DDR3 數據處理

- 萊迪思半導體公司(NASDAQ: LSCC)與Helion今天宣布他們已經發布知識產權(IP)核用于視頻安全和監控攝像機市場。針對LatticeXP2™、LatticeECP2M™和LatticeECP3™FPGA系列,Helion展示了其IONOS流水線型視頻IP和Vesta評估平臺。Helion Vesta評估平臺是一個完全獨立的平臺,能夠開發和實現針對攝像機系統的圖像流水線技術,尤其是緊湊形式的視頻安全應用,如網絡IP和球型攝像機。

Helion的Ves

- 關鍵字:

Lattice 視頻監控 視頻安全 IP核

- IP(IntellectualPropcrty)就是常說的知識產權。美國Dataquest咨詢公司將半導體產業的IP定義為用于ASIC...

- 關鍵字:

IP核 晶閘管 EDA VHDL

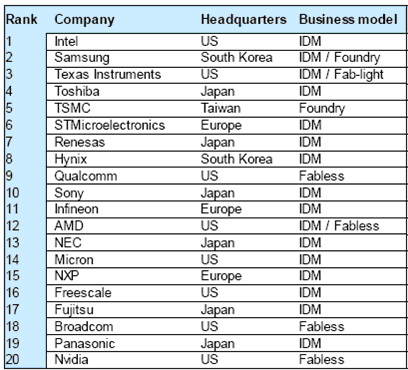

- 在幾年前如果有人將ARM和Intel相提并論,一定會被同行恥笑。Intel是一家年銷售額過300億美金,每年研發投入超過50億美元,在全球擁有近10萬員工的IT巨頭,而ARM僅僅是一家“著名的小公司”,其銷售額僅僅幾個億美金而已,在全球擁有不到2000名員工。但今天,當Intel要大力拓展嵌入式市場,極力宣傳其處理器極其適用于嵌入式應用的時候,卻遇到了一個繞不過的競爭對手,ARM。其實,Intel面對的絕不僅僅是一家ARM公司,它面對的是一個ARM公司營造起來的生態系統。

半

- 關鍵字:

Intel ARM IP核 生態價值

- 摘要: 重點闡述了USB接口IP核關鍵模塊的設計和驗證,用VerilogHDL對USBIP核協議RTL級代碼編寫,對USB協議的數據流、傳輸等進行了深入的分析,在Xilinx ISE軟件平臺上進行了FPGA綜合,并在Xilinx FPGA開發板上調試成功

- 關鍵字:

FPGA USB IP核 接口

- 亮相IIC-China 2010,聚焦自主知識產權

Tensilica將于3月15-16日亮相上海IIC-China 2010(國際集成電路研討會暨展覽會)。針對金融危機對半導體產業的影響、半導體廠商在研發成本方面的問題以及領先的中國半導體廠商對于自主知識產權的孜孜追求,Tensilica 在本屆展會上將著重展示其可配置處理器在幫助企業研發自主知識產權方面的卓越表現(展位號:8S35)。Tensilica亞太區總監黃啟弘將在高峰論壇做出“Tensilica靈活配置的DSP,幫您實現自主知

- 關鍵字:

自主知識產權 Xtensa ConnX DSP IP核

- 1 引言 隨著半導體工藝的發展,片上系統SOC已成為當今一種主流技術。基于IP復用的SOC設計是通過用戶自定義邏輯(UDL)和連線將IP核整合為一個系統,提高了設計效率,加快了設計過程,縮短了產品上市時間。但是隨著設

- 關鍵字:

BIST 編譯碼器 IP核 測試

- 設計基于FPGA的8段數碼管動態顯示IP核,介紹8段數碼管內部結構及其驅動顯示方式和IP核設計方法,給出8段數碼管動態顯示IP核的Verilog HDL程序源代碼及其C語言驅動程序。此IP核可例化成1~8個共陰極(或共陽極)數碼管控制器,能方便地控制1~8個數碼管同時顯示數字和小數點位。測試結果表明,該IP核工作可靠、穩定,可直接應用于電子設計中。

- 關鍵字:

FPGA 8段數碼管 動態顯示 IP核

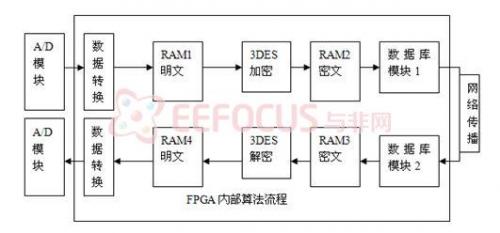

- 信息社會中,基于密碼算法設計的安全芯片,能夠為用戶的敏感信息提供有效的機密性與完整性保護。信息化的不斷深入使得人們對信息安全服務的需求呈現使用簡單化、功能多樣化、高度集成化等趨勢。這要求安全芯片在

- 關鍵字:

安全芯片 IP核 密碼算法 集成方法

- 引 言

SoC設計的快速發展是以IP核復用為基礎的。IP核的復用極大地提高了SoC系統設計的開發效率,SoC 片上總線的選擇是IP核間集成與互連的關鍵技術之一。目前片上總線的標準協議眾多,如ARM公司提出的AMBA總線

- 關鍵字:

AMBA SOC 息線 IP核

- 隨著電路復雜性的增加,越來越多的設計者開始采用擁有知識產權的、設計良好的功能模塊來加快系統開發。因此,需要相應的技術手段保護這些功能模塊不被非法復制、篡改或竊取。針對FPGA開發中的知識產權保護問題,提出一種結合EDA軟件和FPGA的IP(Intellectual Proterty)核保護方法,有效的防止IP核被竊取,以及防止最終在FPGA上實現設計的非法復制。

- 關鍵字:

FPGA EDA 軟件 IP核

ip核介紹

IP核概述

IP核則是一段具有特定電路功能的硬件描述語言程序,該程序與集成電路工藝無關,可以移植到不同的半導體工藝中去生產集成電路芯片。利用IP核設計電子系統,引用方便,修改基本元件的功能容易。具有復雜功能和商業價值的IP核一般具有知識產權,盡管IP核的市場活動還不規范,但是仍有許多集成電路設計公司從事IP核的設計、開發和營銷工作。IP核有兩種,與工藝無關的VHDL程序稱為軟核;具有特定電路 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473