EEPW首頁(yè) >>

主題列表 >>

fsp:fpga-pcb

fsp:fpga-pcb 文章 最新資訊

協(xié)同設(shè)計(jì),未來硬件設(shè)計(jì)工作的方向

- Mentor Graphics PCB Technology Forum 2012 China北京站活動(dòng)在前不久舉行。此次活動(dòng)探討了PCB設(shè)計(jì)在產(chǎn)品研發(fā)過程中的重要性、PCB設(shè)計(jì)中的IP管理、高速設(shè)計(jì)解決方案以及Mentor Graphics的協(xié)作型PCB設(shè)計(jì)方案等主題。 目前,對(duì)于PCB設(shè)計(jì)工作的最大挑戰(zhàn)是:隨著產(chǎn)品功能和性能等方面的不斷提升,PCB板的布線規(guī)模也越來越大,越來越復(fù)雜,需要考慮的因素也越來越多,提高PCB設(shè)計(jì)時(shí)的工作效率,成了最大的關(guān)鍵挑戰(zhàn)。 在過去,PCB板的復(fù)雜度并沒

- 關(guān)鍵字: Mentor Graphics PCB 并行設(shè)計(jì)

電力線仿真系統(tǒng)的FPGA設(shè)計(jì)與實(shí)現(xiàn)

- 摘要 電力線通信設(shè)備的研發(fā)需要一種標(biāo)準(zhǔn)化的測(cè)試平臺(tái)對(duì)電力線信道進(jìn)行實(shí)時(shí)仿真,通過信道傳輸特性和各種噪聲進(jìn)行全面的測(cè)試和驗(yàn)證,而目前缺乏這樣的平臺(tái)。文中對(duì)電力線信道傳輸特性和噪聲進(jìn)行了深入研究,并在此基礎(chǔ)

- 關(guān)鍵字: 設(shè)計(jì) 實(shí)現(xiàn) FPGA 系統(tǒng) 仿真 電力線

單片機(jī)與FPGA實(shí)現(xiàn)等精度頻率測(cè)量和IDDS技術(shù)設(shè)計(jì)方

- O.引言本系統(tǒng)利用單片機(jī)和FPGA有效的結(jié)合起來共同實(shí)現(xiàn)等精度頻率測(cè)量和IDDS技術(shù),發(fā)揮各自的優(yōu)點(diǎn),使設(shè)計(jì)變得更加容易和靈活,并具有頻率測(cè)量范圍寬、產(chǎn)生的波形頻率分辨率高及精度大等特點(diǎn)。系統(tǒng)方便靈活,測(cè)量精度

- 關(guān)鍵字: FPGA IDDS 單片機(jī) 等精度頻率測(cè)量

一種基于FPGA的慢門限恒虛警處理電路設(shè)計(jì)

- 摘要 雷達(dá)信號(hào)的檢測(cè)多是在干擾背景下進(jìn)行,如何從干擾中提取目標(biāo)信號(hào),不僅要求有一定的信噪比,而且必需有恒虛警處理設(shè)備。恒虛警處理是雷達(dá)信號(hào)處理的重要組成部分,慢門限恒虛警處理主要是針對(duì)接收機(jī)熱噪聲,文中

- 關(guān)鍵字: FPGA 慢門限 恒虛警處理 電路設(shè)計(jì)

基于FPGA的高速數(shù)據(jù)采集控制模塊設(shè)計(jì)

- 摘要 以Spartan-3E系列FPGA為核心控制模塊,結(jié)合AD10242模數(shù)轉(zhuǎn)換芯片和MXP-123MD-F光收發(fā)模塊,實(shí)現(xiàn)了高速數(shù)據(jù)采集和光纖傳輸 其中FPGA用于實(shí)現(xiàn)數(shù)據(jù)控制、雙口RAM和8B/10B編解碼等功能。該數(shù)據(jù)采集控制模塊具有性能

- 關(guān)鍵字: FPGA 高速數(shù)據(jù) 采集控制 模塊設(shè)計(jì)

CADENCE PCB設(shè)計(jì)技術(shù)方案

- CADENCE PCB設(shè)計(jì)解決方案能為解決與實(shí)現(xiàn)高難度的與制造密切相關(guān)的設(shè)計(jì)提供完整的設(shè)計(jì)環(huán)境,該設(shè)計(jì)解決方案集成了從設(shè)計(jì)構(gòu)想至最終產(chǎn)品所需要的一切設(shè)計(jì)流程,包含設(shè)計(jì)輸入元件庫(kù)工具、PCB編輯器和一個(gè)自動(dòng)/交互連布線

- 關(guān)鍵字: CADENCE PCB 設(shè)計(jì)技術(shù) 方案

導(dǎo)出PCB設(shè)計(jì)軟件坐標(biāo)數(shù)據(jù)的方法(二)

- 2.6 CadstarCadstar 是日本 Zuken 公司推出的面向中低端用戶的電路板設(shè)計(jì)軟件,其市場(chǎng)定位與 PADS 軟件相似,但市場(chǎng)占有率遠(yuǎn)不及 PADS,主要在一些日本及臺(tái)灣公司使用,目前最新版本號(hào) 9.0,其坐標(biāo)數(shù)據(jù)導(dǎo)出步驟如下

- 關(guān)鍵字: PCB 設(shè)計(jì)軟件 方法 坐標(biāo)數(shù)據(jù)

導(dǎo)出PCB設(shè)計(jì)軟件坐標(biāo)數(shù)據(jù)的方法(一)

- 本文將詳細(xì)介紹所有常見PCB設(shè)計(jì)軟件坐標(biāo)數(shù)據(jù)的導(dǎo)出方法及步驟,以給從事相關(guān)工作的工藝技術(shù)人員提供參考。現(xiàn)代電子生產(chǎn)企業(yè)的設(shè)計(jì)部門幾乎全部采用PCB軟件進(jìn)行電路設(shè)計(jì),生產(chǎn)制造部門也大量使用貼片機(jī)、插件機(jī)等自動(dòng)

- 關(guān)鍵字: PCB 設(shè)計(jì)軟件 方法 坐標(biāo)數(shù)據(jù)

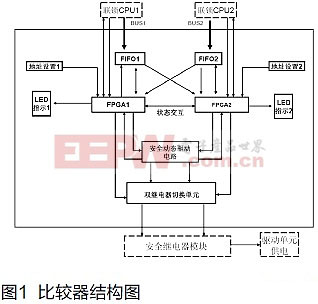

基于FPGA的二取二總線數(shù)據(jù)比較器

- 摘要:基于FPGA的二取二總線數(shù)據(jù)比較器實(shí)現(xiàn)聯(lián)鎖邏輯運(yùn)算的兩塊CPU板總線數(shù)據(jù)的實(shí)時(shí)校核。在兩條總線數(shù)據(jù)比較一致且總線數(shù)據(jù)的CRC校核通過時(shí)兩個(gè)FPGA分別輸出互為反相的動(dòng)態(tài)脈沖,板上驅(qū)動(dòng)電路輸出信號(hào)控制板外供電繼電器對(duì)聯(lián)鎖系統(tǒng)驅(qū)動(dòng)單元供電,否則通過停止輸出動(dòng)態(tài)脈沖在50ms內(nèi)切斷供電繼電器。

- 關(guān)鍵字: FPGA CPU 201206

基于FPGA的信號(hào)頻譜分析系統(tǒng)

- 摘要 利用FPGA實(shí)現(xiàn)了信號(hào)的采集與頻譜分析系統(tǒng),對(duì)系統(tǒng)進(jìn)行了模塊劃分,并分別給出了各模塊的設(shè)計(jì)要點(diǎn),完成了模擬信號(hào)采集模塊、快速傅里葉變換模塊、存儲(chǔ)模塊以及VGA顯示模塊的設(shè)計(jì)。最后對(duì)設(shè)計(jì)的各模塊進(jìn)行了功能

- 關(guān)鍵字: FPGA 信號(hào)頻譜分析 系統(tǒng)

fsp:fpga-pcb介紹

您好,目前還沒有人創(chuàng)建詞條fsp:fpga-pcb!

歡迎您創(chuàng)建該詞條,闡述對(duì)fsp:fpga-pcb的理解,并與今后在此搜索fsp:fpga-pcb的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fsp:fpga-pcb的理解,并與今后在此搜索fsp:fpga-pcb的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司