- 為了給實際應用中選擇合適FIR濾波器的FPGA實現結構提供參考,首先從FIR數字濾波器的基本原理出發,分析了FIR濾波器的結構特點,然后分別介紹了基于FPGA的FIR濾波器的串行、并行、轉置型、FFT型和分布式結構型的實現方法,對于各種實現的結構做了分析、比較以及優化處理,特別是對基于FFT的FIR濾波器與傳統卷積結構進行了精確的數值計算比較,最后得出滿足于低階或高階的各種FIR濾波器實現結構的適用范圍及其優缺點,并針對實際工程應用提出了下一步需解決的問題。

- 關鍵字:

FPGA FIR 濾波器 實現方法

- 通過對現有編碼算法的改進,提出一種新的編碼算法,它降低功耗的方法是通過減少部分積的數量來實現的。因為乘法器的運算主要是部分積的相加,因此,減少部分積的數量可以降低乘法器中加法器的數量,從而實現功耗的減低。在部分積的累加過程中.又對用到的傳統全加器和半加器進行了必要的改進,避免了CMOS輸入信號不必要的翻轉,從而降低了乘法器的動態功耗。通過在Altera公司的FPGA芯片EP2CTOF896C中進行功耗測試,給出了測試結果,并與現有的兩種編碼算法進行了比較。功耗分別降低3.5%和8.4%。

- 關鍵字:

FPGA 24位 低功耗 乘法器

- 本文介紹了一個基于FPGA 的高效率多時鐘的虛擬直通路由器,通過優化中央仲裁器和交叉點矩陣,以爭取較小面積和更高的性能。同時,擴展路由器運作在獨立頻率的多時鐘NoC 架構中,并在一個3×3Mesh 的架構下實驗,分析其性能特點,比較得出多時鐘片上網絡具有更高的性能。

- 關鍵字:

FPGA 多時鐘 片上網絡

- 針對使用硬件描述語言進行設計存在的問題,提出一種基于FPGA并采用DSP BuildIer作為設計工具的數字信號處理器設計方法。并按照Matlab/Simulink/DSP Builder/QuartusⅡ設計流程,設計了一個12階FIR低通數字濾波器,通過Quaxtus時序仿真及嵌入式邏輯分析儀signalTapⅡ硬件測試對設計進行了驗證。結果表明,所設計的FIR濾波器功能正確,性能良好。

- 關鍵字:

Builder FPGA DSP 數字信號處理器

- 本文提供的解決方案可防止FPGA設計被拷貝,即使配置比特流被捕獲,也可以保證FPGA設計的安全性。通過在握手令牌由MAX II器件傳送給FPGA之前,禁止用戶設計功能來實現這種安全性。選用MAX II器件來產生握手令牌,這是因為該器件具有非易失性,關電時可保持配置數據。而且,對于這種應用,MAX II器件是最具成本效益的CPLD。本文還介紹了采用這種方案的一個參考設計。

- 關鍵字:

FPGA MAX 器件 方案

- 針對傳統集成電路(ASIC)功能固定、升級困難等缺點,利用FPGA實現了擴頻通信芯片STEL-2000A的核心功能。使用ISE提供的DDS IP核實現NCO模塊,在下變頻模塊調用了硬核乘法器并引入CIC濾波器進行低通濾波,給出了DQPSK解調的原理和實現方法,推導出一種簡便的引入π/4固定相移的實現方法。采用模塊化的設計方法使用VHDL語言編寫出源程序,在VIrtex-II Pro開發板上成功實現了整個系統。測試結果表明該系統正確實現了STEL-2000A的核心功能。

- 關鍵字:

STEL 2000 FPGA 擴頻通信

- 波長信號的解調是實現光纖光柵傳感網絡的關鍵,基于現有的光纖光柵傳感器解調方法,提出一種基于FPGA的雙匹配光纖光柵解調方法,此系統是一種高速率、高精度、低成本的解調系統,并且通過引入雙匹配光柵有效地克服了雙值問題同時擴大了檢測范圍。分析了光纖光柵的測溫原理并給出了該方案軟硬件設計,綜合考慮系統的解調精度和FPGA的處理速度給出了基于拉格朗日的曲線擬合算法。

- 關鍵字:

FPGA 光纖光柵 解調系統

- 為滿足用戶的多種設計需求,Altera公司 今天發布其28-nm器件系列產品,為業界提供最全面的器件選擇。Altera在Cyclone V和Arria V FPGA新系列、最新擴展的Stratix V FPGA以及此前發布的HardCopy V ASIC系列中為用戶提供突出不同產品優勢的解決方案。

- 關鍵字:

Altera Stratix V FPGA

- 摘要:經典的碼盤數字測速方法有M法、T法、M/T法,但都有一定的不足。為了克服原有方法的不足,設計并實現了一種在較大速度范圍都有良好精度和良好快速性的測速方法。電路采用FPGA實現,測速得到的數據通過PCI總線從

- 關鍵字:

FPGA PCI 高精度 測速

- 采用FPGA的模擬動態濾波器,在結構上簡易,性能上穩定,測試和設計都十分的方便。FPGA的使用,能根據具體要求很方便的改變控制信號,同時實現超聲診斷儀中多個模塊并行工作,也為以后的更多模擬部分數字化提供了基礎。

- 關鍵字:

FPGA 超聲診斷儀 動態 濾波器

- 本文分析了IL-E2型TDI-CCD 芯片的工作過程和對驅動信號的要求,在此基礎上設計出合理的時序電路, 為了滿足在實際工作中像移速度異速匹配的要求,在時序電路的設計中時序發生部分是可調的。這種設計方案簡單、可靠、實用。

- 關鍵字:

FPGA CCD 相機 時序

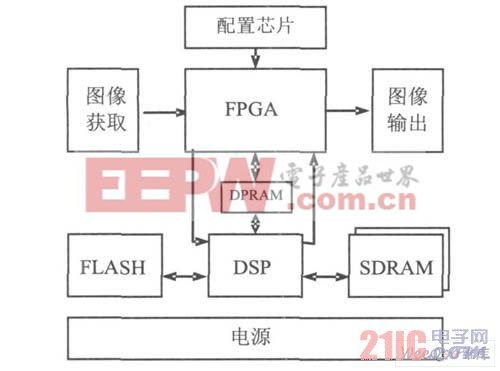

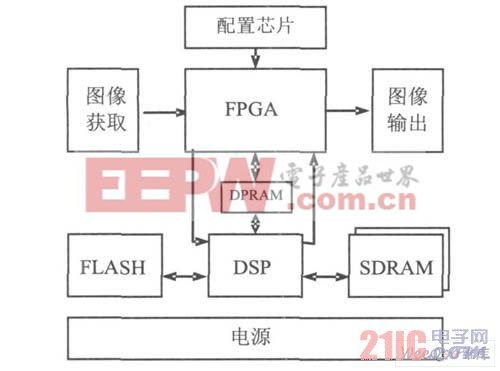

- 基于FPGA+ DSP的實時圖像處理系統設計與實現,摘 要: 針對圖像處理系統計算量大、實時性高和體積小的要求, 研制了一種以DSP為主處理器FPGA 為輔處理器的高性能實時圖像處理系統。利用這兩種芯片的各自特點, 將算法分成兩部分分別交由FPGA 和DSP處理, 大大提高

- 關鍵字:

FPGA,DSP

fpga-spartan介紹

您好,目前還沒有人創建詞條fpga-spartan!

歡迎您創建該詞條,闡述對fpga-spartan的理解,并與今后在此搜索fpga-spartan的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473