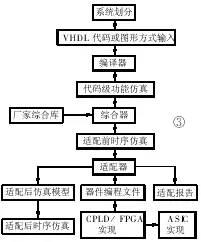

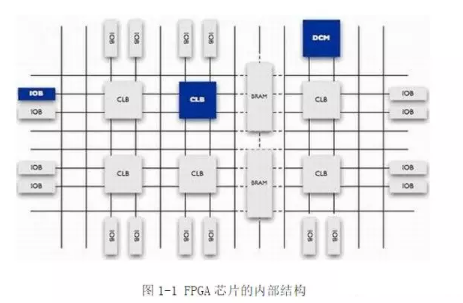

FPGA是可編程芯片,因此FPGA的設計方法包括硬件設計和軟件設計兩部分。硬件包括FPGA芯片電路、存儲器、輸入輸出接口電路以及其他設備,軟件即是相應的HDL程序以及最新才流行的嵌入式C程序。硬件設計是基礎,但其方法比較固定,本書將在第4節對其進行詳細介紹,本節主要介紹軟件的設計方法。 目前微電子技術已經發展到SOC階段,即集成系統(Integrated System)階段,相對于集成電路(IC)的設計思想有著革命性的變化。SOC是一個復雜的系統,它將一個完整產品的功能集成在一個芯片上,包

關鍵字:

FPGA

最近的幾篇論文都改好投出去了,希望后面有好的結果。暫時也就有點閑暇時間空出來了,好久沒有寫技術文章來總結提煉一下了,今天難得就寫一點。 每年到了找工作的時節,總會有很多迷茫的小本甚至是小碩在到處訊問說:我是不是應該去參加個培訓班,去學一門什么什么技術。然后學哪個比較好找工作一點,學哪個收入會高一點等等。每當這個時候就有很多抱著就業目的的人來問到底學什么技術好啊,哪個技術有前途啊,等等。 一般在這個時候,我是不推薦這幫人去學習FPGA的。當然,并不是FPGA技術不好,也不是學FPGA技術沒有前途,而

關鍵字:

FPGA SoC

中國濟南,2018年3月19日訊,山東高云半導體科技有限公司(以下簡稱“高云半導體”)今日宣布推出高云 FPGA四路并行離線燒錄器(以下簡稱“離線燒錄器”),支持高云半導體小蜜蜂家族GW1N(R)系列芯片數據流文件的離線燒錄。 圖一 離線燒錄器外觀圖 離線燒錄器(圖一)是指在脫離PC環境下對GW1N(R)芯片進行數據燒錄的設備,具備速度快、數據保密、便攜穩定、多路燒錄等特點,適用于工廠大批量、快速量產,并方便檢修人員外出攜帶;相比傳統的PC終端,離線燒錄器優勢顯著。 其一,離

關鍵字:

高云 FPGA

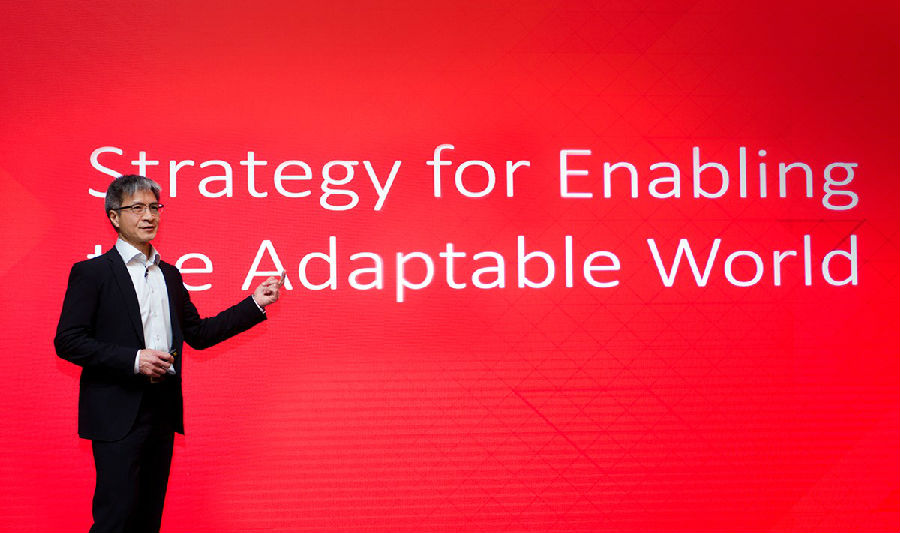

2018年一月,賽靈思迎來了第四任總裁Victor Peng。Victor Peng此前擔任賽靈思COO(首席運營官),負責賽靈思公司全球銷售、產品和垂直市場、產品的開發以及全球運營和質量工作。在此之前,他曾任賽靈思產品執行副總裁兼總經理,負責公司產品組合與差異性技術的定義、開發以及產品市場營銷,實現了連續三代核心產品的領先地位,于2017年10月成為董事會成員之一。

關鍵字:

Xilinx FPGA ACAP

自適應和智能計算的全球領先企業賽靈思公司(Xilinx,?Inc.)總裁兼首席執行官(CEO)Victor?Peng?,今天揭示了公司的未來愿景與戰略藍圖。Peng?的愿景旨在為賽靈思帶來新發展、新技術和新方向,打造“自適應計算加速平臺”。在該世界中,賽靈思將超越?FPGA?的局限,推出高度靈活且自適應的全新處理器及平臺產品系列,為用戶從端點到邊緣再到云端多種不同技術的快速創新提供支持。 圖一?賽靈思CEO?Victor

關鍵字:

Xilinx FPGA

大學時代第一次接觸FPGA至今已有10多年的時間,至今記得當初第一次在EDA實驗平臺上完成數字秒表、搶答器、密碼鎖等實驗時那個興奮勁。當時由于沒有接觸到HDL硬件描述語言,設計都是在MAX+plus II原理圖環境下用74系列邏輯器件搭建起來的。

后來讀研究生,工作陸陸續續也用過Quartus II、FoundaTIon、ISE、Libero,并且學習了verilogHDL語言,學習的過程中也慢慢體會到verilog的妙用,原來一小段語言就能完成復雜的原理圖設計,而且語言的移植性可操作性比原理圖

關鍵字:

FPGA Verilog

作為國內領先的可編程邏輯器件供應商,廣東高云半導體科技股份有限公司(以下簡稱“高云半導體”)今日宣布成立香港研發中心,新成立的研發中心位于香港科學園二期浚湖樓,這是繼濟南、上海、廣州、美國硅谷四大研發中心之后,高云半導體成立的第五大研發中心。

“在香港科學園設立研發中心,將為高云半導體在國際市場開拓,創新合作等方面提供重要的技術支持,”高云半導體CEO朱璟輝介紹,“作為一個創新驅動型的公司,高云將在香港打造一個實力雄厚的研發與技術支

關鍵字:

高云 FPGA

中國香港,2018年3月12日,作為國內領先的可編程邏輯器件供應商,廣東高云半導體科技股份有限公司(以下簡稱“高云半導體”)今日宣布成立香港研發中心,新成立的研發中心位于香港科學園二期浚湖樓,這是繼濟南、上海、廣州、美國硅谷四大研發中心之后,高云半導體成立的第五大研發中心。

關鍵字:

FPGA 高云半導體

我們(IEEE)最近與Bunny Huang進行了有趣的交流,他是硬件大師以及Chumby,NetTV和Novena Laptop等的創造者。他還是Hacking the Xbox,The Essential Guide to Electronics in Shenzhen兩篇文章的作者,在IEEE Spectrum中有兩篇專題文章。 我們感興趣的是Huang的意見,一個小的資金適中的團隊,

關鍵字:

芯片 FPGA

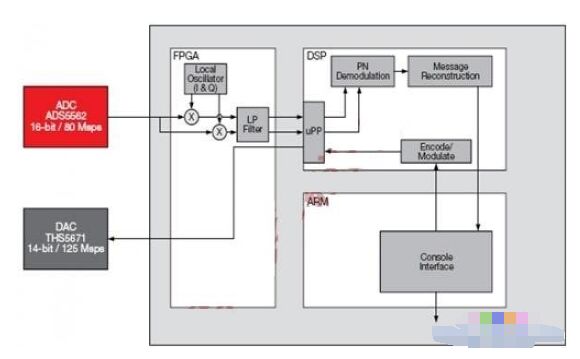

CritICal Link公司的某客戶需要針對多個應用開發一個擴頻無線電收發器。該客戶已經開發出一套算法,準備用于對信號進行調制和解調,但他們卻缺少構建完整系統的資源和專業知識。客戶希望利用軟件定義無線電(SDR)系統的靈活性優勢。本文將探討如何基于德州儀器(TI)的OMAP-L138 DSP+ARM處理器與FPGA來實現該系統。 平臺 Critical Link選擇其MityDSP-L138F嵌入式系統模塊作為SDR的基礎,因為該模塊不僅具有很強的處理能力,而且可以

關鍵字:

FPGA ARM

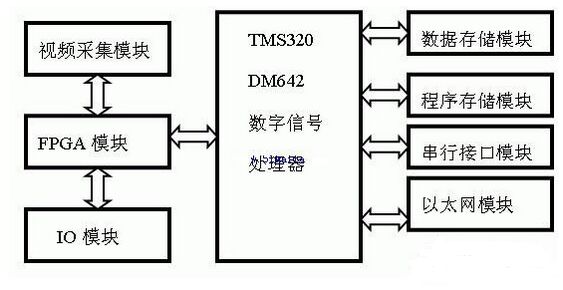

本文將機器視覺與網絡技術相結合,使用TI公司新近推出的6000系列DSPsTMS320DM642為核心,應用ALTERA公司的FPGA,用其實現圖像預處理,減輕了DSPs的負擔。應用網絡技術實現圖像傳輸。 1、引言 機器視覺自起步發展到現在,已有15年的發展歷史。應該說機器視覺作為一種應用系統,其功能特點是隨著工業自動化的發展而逐漸完善和發展的。 目前,國際上視覺系統的應用方興未艾,1998年的市場規模為46億美元。在國外,機器視覺的應用普及主要體現在半導體及電子行業,其中大概 40%

關鍵字:

DSP FPGA

新的一年開啟新的希望,新的空白承載新的夢想。這是年初一集微網給讀者們拜年時寫的寄語。在中國農歷新年開年之際,半導體產業里也迎來了許多新的起點。例如長江存儲在與蘋果就采購前者的Nand閃存芯片一事談判,又例如前京微雅格副總裁王海力堅守18個月后的二次創業。

2005年年底,即將從清華大學計算機專業博士畢業的王海力加入了一家新成立的中外合資公司——雅格羅技,開始了國產FPGA芯片研發。2010年在北京市政府相關引導資金支持下,該公司也轉換身份并更名為“京微雅格&r

關鍵字:

京微雅格 FPGA

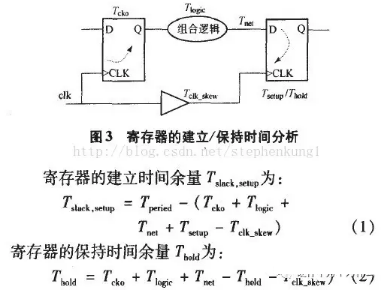

10、FPGA的時序基礎理論 我們的分析從下圖開始,下圖是常用的靜態分析結構圖,一開始看不懂公式不要緊,因為我會在后面給以非常簡單的解釋: 這兩個公式是一個非常全面的,準確的關于建立時間和保持時間的公式。其中Tperiod為時鐘周期;Tcko為D觸發器開始采樣瞬間到D觸發器采樣的數據開始輸出的時間;Tlogic為中間的組合邏輯的延時;Tnet為走線的延時;Tsetup為D觸發器的建立時間;Tclk_skew為時鐘偏移,偏移的原因是因為時鐘到達前后兩個D觸發器的路線不是一樣長。 這里我們來做如下轉

關鍵字:

FPGA 時序

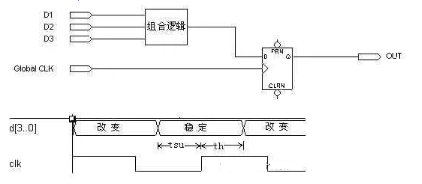

8、FPGA時鐘系統 1. FPGA的全局時鐘是什么? FPGA的全局時鐘應該是從晶振分出來的,最原始的頻率。其他需要的各種頻率都是在這個基礎上利用PLL或者其他分頻手段得到的。 2. 全局時鐘和BUFG: BUFG,輸入為固定管腳,輸出為H型全銅全局高速網絡,這樣抖動和到任意觸發器的延時差最小,這個也就是FPGA做同步設計可以不需要做后仿真的原因。 全局時鐘:今天我們從另一個角度來看一下時鐘的概念:時鐘是D觸發器的重要組成部分,一個有效邊沿使得D觸發器進行一次工作。而更多的時候,D觸發器保

關鍵字:

FPGA 時鐘

1、查找表LUT和編程方式 第一部分: 查找表LUT FPGA是在PAL、GAL、EPLD、CPLD等可編程器件的基礎上進一步發展的產物。它是作為ASIC領域中的一種半定制電路而出現的,即解決了定制電路的不足,又克服了原有可編程器件門電路有限的缺點。 由于FPGA需要被反復燒寫,它實現組合邏輯的基本結構不可能像ASIC那樣通過固定的與非門來完成,而只能采用一種易于反復配置的結構。查找表可以很好 地滿足這一要求,目前主流FPGA都采用了基于SRAM工藝的查找表結構,也有一些軍品和宇航級FPGA采用

關鍵字:

FPGA CPLD

fpga:quartusⅡ介紹

您好,目前還沒有人創建詞條fpga:quartusⅡ!

歡迎您創建該詞條,闡述對fpga:quartusⅡ的理解,并與今后在此搜索fpga:quartusⅡ的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473