圖像傳感器,或稱感光元件,是一種將光學圖像轉換成電子信號的設備,它被廣泛地應用在數碼相機和其他電子光學設備中。早期的圖像傳感器采用模擬信號,如攝像管(video camera tube)。如今,圖像傳感器主要分為感光耦合元件(charge-coupled device, CCD)和互補式金屬氧化物半導體有源像素傳感器(CMOS Active pixel sensor)兩種。本文介紹基于CMOS或CCD兩種圖像傳感器的應用及技術文獻,供大家參考。

基于USB傳輸及CMOS圖像傳感器的指紋識別儀的實

關鍵字:

Verilog HDL QuartusⅡ VHDL

汽車在給人們生活帶來便利的同時也帶來了交通事故。其中超速行駛是造成交通事故的重要隱患之一。據研究表明,目前針對車輛超速行駛情況的道路抓拍系統中所使用的圖像傳感器大多為小面陣器件,普遍為100萬~200萬像素,從而導致抓拍圖像的像素比較低、能夠同時抓拍的車道數較少等等問題。面對這一系列問題,大面陣的圖像傳感器便逐漸成了人們關注的熱點。在設計過程中,分析了具有500萬像素的CMOS圖像傳感器MT9P401的工作模式,選用QuartusⅡ做為開發工具,使用Verilog HDL語言對驅動電路設計方案進行了硬

關鍵字:

FPGA 圖像傳感器

當人們考慮有兩個圖像傳感器的應用時,首先很可能想到的是一個三維攝相機。不過,也有許多設計可以通過使用來自兩個圖像傳感器的數據進行改善;一個例子是汽車司機錄像機(CDR)的黑盒子,這通常是安裝在后視鏡附近,擁有兩個攝像機(圖1)。一個攝像機朝向擋風玻璃,而另一個攝像機指向司機。在本地的存儲器芯片中存儲攝像機的視頻,如果有意外事故或疑問,可以進行檢索。

基于FPGA的雙圖像傳感器設計方案.pdf

關鍵字:

FPGA 圖像傳感器

就算你代碼再怎么牛逼,硬件描述語言再怎么熟練,沒有認知FPGA的工作原理,一切都是浮云。因此,在真正開始實戰演練之前,Bingo將首先介紹FPGA最小工作配置要求,以及一些基本的外設,并通過DIY CPLD/FPGA系統板案例的分析講解,用淺顯易懂的語言,讓初學者深刻認識CPLD/FPGA的工作原理,能夠有一個更深刻的軟硬件思維。

一、Altium Designer 09 winter 軟件介紹

Layout的軟件有很多,包括Altium Designer、P

關鍵字:

FPGA CPLD DIY

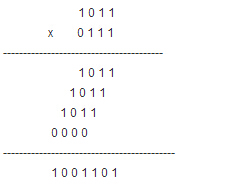

上次看了一下關于乘法器的Verilog代碼,有幾個地方一直很迷惑,相信很多初學者看這段代碼一定跟我當初一樣,看得一頭霧水,在網上也有一些網友提問,說這段代碼不好理解,今天小墨同學就和大家一起來看一下這段代碼,我會親自在草稿紙上演算,盡量把過程寫的詳細些,讓更多的人了解乘法器的設計思路。

下面是一段16位乘法器的代碼,大家可以先瀏覽一下,之后我再做詳細解釋

module mux16(

clk,rst_n,

start,ain,bin,yout,done

);

inpu

關鍵字:

FPGA Verilog 時序邏輯

Nios Ⅱ嵌入式處理器是ALTERA公司推出的采用哈佛結構、具有32位指令集的第二代片上可編程的軟核處理器, 其最大優勢和特點是模塊化的硬件結構, 以及由此帶來的靈活性和可裁減性。本文基于Nios Ⅱ介紹20款經典設計方案,供大家參考。

基于NiosⅡ的U盤安全控制器設計

本文針對U盤的安全隱患,分析目前較為常見的解決方法,利用SoPC技術,設計實現了一款基于NiosⅡ處理器的U盤安全控制器。該控制器位于PC機和U盤之間,通過對U盤進行扇區級的加解密操作,將普通U盤升級為安全U盤,保證U

關鍵字:

ALTERA FPGA SoPC

引言

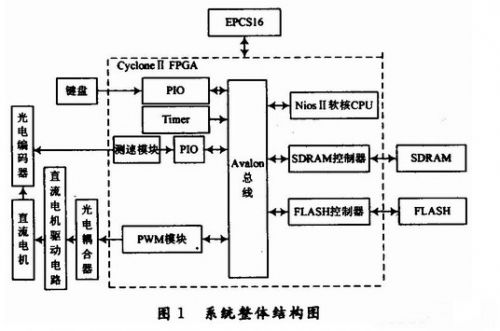

以往的直流電機調速系統通常采用單片機或DSP進行控制,而單片機需要使用大量的外圍電路,且系統的可升級性差,如更換控制器,往往要對整個軟硬件進行重新設計,可重用性不高。而采用DSP作為主要控制器,如果碰到處理多任務系統時,一片DSP不能勝任,這時就需要再擴展一片DSP或者FPGA芯片來輔助控制,從而實行雙芯片控制模式。但這樣做,既增加了兩個處理器之間同步和通信的負擔,又使系統實時性變壞,延長系統開發時間。基于以上此類問題,本文提出了采用Altera公司推出的NiosⅡ軟核來控制直流電機調速系

關鍵字:

PID NiosⅡ FPGA

系統以FPGA為核心,通過對正弦信號進行濾波、放大整形后得到標準的方波,由FPGA對其頻率、周期及相位差進行測量。頻率、周期測量采用等精度測量法,其具有精度高的特點;相位差測量采用鑒相器分辨出相位差后測量其高電平所占比例測量。摒棄傳統的FPGA+單片機方案,利用SOPC Builder在FPGA上構建Nios Ⅱ處理器對測量的數據進行數據處理及顯示,實現了頻率、周期、相位差測量的片上系統(SOPC),提高了系統的穩定性、降低了布線難度。

基于Nios_處理器的多功能計數器系統設計.pdf

關鍵字:

NiosⅡ 多功能計數器 FPGA

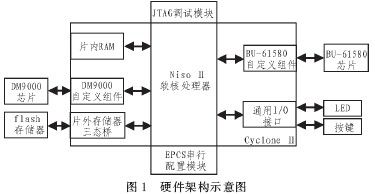

自2005年9月LXI總線推出以來,已經顯示出其組建測試系統的眾多優點。基于LXI總線組建測試系統具有易于使用、靈活性高、模塊化和可擴縮性、實現更快的系統吞吐率、可分布式應用、長壽命、低成本、通過IEEE1588時鐘同步、機架空間小、合成儀器等諸多優點。

1553B總線的全名為“時分制指令/響應式多路傳輸數據總線”,國內多型戰斗機、軍艦等武器平臺都采用其作為傳輸總線。因此研制基于LXI總線的1553B通訊模塊,不僅能滿足多型武器裝備對1553B總線的測試需求,也對LXI總

關鍵字:

NiosⅡ 1553B FPGA

京微雅格是世界上除美國硅谷以外唯一自主研發并成功量產現場可編程邏輯(FPGA)芯片的公司,目前擁有數百項技術專利和近百款產品。目前,已經有越來越多的用戶都開始使用國產FPGA來做自己的設計,然而在FPGA的開發過程中,免不了要對設計進行仿真。京微雅格的FPGA是支持在modelsim中進行仿真的。

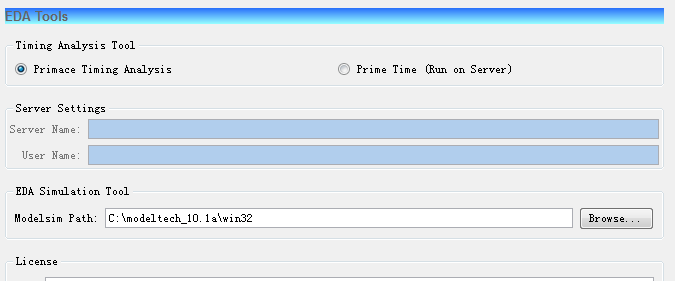

京微雅格的FPGA需要在Primace軟件中進行開發,為了便于客戶進行仿真設計,在Primace5.0及以上版本都支持在工程中直接調用仿真工具Modelsim。同時,也支持在modelsim中直接進行

關鍵字:

京微雅格 FPGA 仿真

Spartan-3 FPGA能以突破性的價位點實現嵌入式DSP功能。本文闡述了Spartan-3 FPGA針對DSP而優化的特性,并通過實現示例分析了它們在性能和成本上的優勢。

所有低成本的FPGA都以頗具吸引力的價格提供基本的邏輯性能,并能滿足廣泛的多用途設計需求。然而,當考慮在FPGA構造中嵌入DSP功能時,必須選擇高端FPGA以獲得諸如嵌入式乘法器和分布式存儲器等平臺特性。

Spartan-3 FPGA的面世改變了嵌入式DSP的應用前景。雖然Spartan-3系列器件的價位可能較低,

關鍵字:

賽靈思 FPGA Spartan-3

橫跨多重電子應用領域、全球領先的半導體供應商意法半導體(STMicroelectronics,簡稱ST)宣布對基于射線跟蹤 (ray-tracing) 技術的實驗性3D圖形應用系統進行測試驗證。該解決方案采用一顆與現場可編程門陣列 (FPGA, Field-Programmable Gate Array) 相連、基于ARM®處理器的測試芯片。FASTER 研發項目以“簡化分析合成技術,實現有效配置”為目標,是意法半導體與米蘭理工大學 (Politecnico di Mi

關鍵字:

意法半導體 FPGA GPU

一、Altera Quartus II 11.0套件介紹

所謂巧婦難為無米之炊,再強的軟硬件功底,再多的思維創造力,沒有軟件的平臺,也只是徒勞。因此,一切創造的平臺——Quartus II 軟件安裝,由零開啟的世界,便從此開始。

自從Bingo 2009年開始接觸FPGA,Quartus II 版本的軟件從n年前的5.1版本到今天的最新發布的11.0,都使用過;當然對于軟件核心構架而言,萬變不離其宗。雖然多多少少有點bug,但這10多個版本發展到了現在,能看到Alt

關鍵字:

FPGA Quartus II

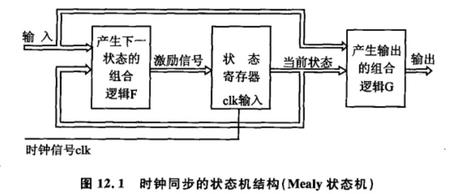

今天我們來寫狀態機。

關于狀態機呢,想必大家應該都接觸過,通俗的講就是數電里我們學的狀態轉換圖。狀態機分為兩中類型,一種叫Mealy型,一種叫Moore型。前者就是說時序邏輯的輸出不僅取決于當前的狀態,還取決于輸入,而后者就是時序邏輯的輸出僅僅取決于當前的狀態。下面兩個圖分別表示兩種不同的狀態機。

?

?

下面我們就通過代碼來寫一下狀態機,以下面的狀態轉換圖為例

?

首先,是一種典型的狀態機寫法,這種寫法我們稱為

關鍵字:

FPGA 狀態機 Mealy Moore

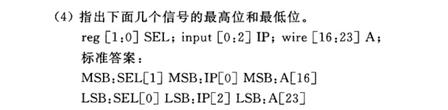

習題呢,來自夏雨聞老師的那本教材,就挑幾個感覺自己做著有點難度的寫寫吧

?

這個題呢剛開始我是沒看明白,記得書上只講了我們習慣上的用法,這種用法我是沒見過,問了下別人才知道,Verilog中一般是左高右低。第一個沒問題,第二個,input [0:2] IP,習慣上我們這樣寫 input [2:0] IP,這里兩個是等價的,即表示第0 .1 .2 三位。第三個,wire [16:23] A,也是,左高右低,表示第16.17.....22. 23位,左高右低就這樣記就好了。

關鍵字:

FPGA 夏雨聞 寄存器

fpga:quartusⅡ介紹

您好,目前還沒有人創建詞條fpga:quartusⅡ!

歡迎您創建該詞條,闡述對fpga:quartusⅡ的理解,并與今后在此搜索fpga:quartusⅡ的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473