- 1.MCU有串口外設的話,在加上電平轉換芯片,如MAX232,SP3485就是RS232和RS485接口了。 2.RS485采用差分信號負邏輯,+2~+6V表示0,-6~-2表示1。有兩線制和四線制兩種接線,四線制是全雙工通訊方式,兩線制是半雙工通訊方式。在RS485一般采用主從通訊方式,即一個主機帶多個從機。 3.Modbus是一種協議標準,可以支持多種電氣接口,如RS232,RS485,也可以在各種介質上傳輸,如雙絞線,光纖,無線。 4.很多MCU的串口都開始自帶FIFO,收發FIFO主要是

- 關鍵字:

MCU

- 如果有一個25美分的MCU,可以用0.5KB的內存做些什么?您現在可能已經使用固定功能的集成電路(IC)很長一段時間了,并且在某些情況下,已經適應了它們有限

- 關鍵字:

25項功能 MCU 集成電路

- 什么樣的積極創新可以幫助您設計出這樣一個系統mdash;mdash;它能夠提醒用戶有兒童在游泳池中溺水,或是有入侵者試圖闖入住宅或者辦公場所?這種技術還

- 關鍵字:

嵌入式 FPGA

- 在日益信息化的現代社會中,計算機和網絡的應用已經全面滲透到日常生活中,各種應用嵌入式系統的電子產品也隨處可見,計算機的應用經過桌面PC系統的空

- 關鍵字:

嵌入式 FPGA

- 人們對寬帶服務的帶寬要求越來越高,促使芯片供應商使用更多的高速串行收發器。因此,下一代應用采用了多種數據速率,從幾Mbps 到數百Gbps,在一種

- 關鍵字:

FPGA ASIC 40 nm

- 1 引言在數字中頻接收機中,把A/D轉換提前到中頻部分,為保證A/D轉換的動態范圍和系統帶寬,要求低噪聲放大器和自動增益控制AGC(Automatic Ga

- 關鍵字:

FPGA AGC 動態范圍 數字

- 要CORDIC(COordination Rotation DIgital Computer)算法實現正交數字混頻器中的數控振蕩器的方法。首先推導了算法產生正余弦信號的實現過程,然后給出了

- 關鍵字:

FPGA 正交數字 混頻器 數控振蕩器

- 本文提出了多級CIC抽取濾波器結構不僅能夠實現更寬輸入信號的任意速率的抽取,并且對帶外信號的衰減也更大。

- 關鍵字:

FPGA 積分 梳狀濾波器

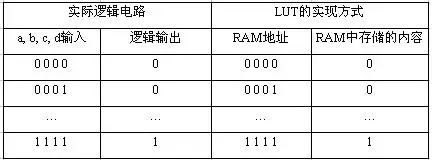

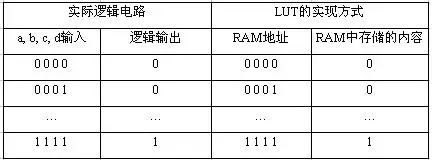

- FPGA工作原理與簡介 如前所述,FPGA是在PAL、GAL、EPLD、CPLD等可編程器件的基礎上進一步發展的產物。它是作為ASIC領域中的一種半定制電路而出現的,即解決了定制電路的不足,又克服了原有可編程器件門電路有限的缺點。 由于FPGA需要被反復燒寫,它實現組合邏輯的基本結構不可能像ASIC那樣通過固定的與非門來完成,而只能采用一種易于反復配置的結構。查找表可以很好地滿足這一要求,目前主流FPGA都采用了基于SRAM工藝的查找表結構,也有一些軍品和宇航級FPGA采用Flash或者熔絲與反熔

- 關鍵字:

FPGA Xilinx Altera

- 常用FPGA/CPLD四種設計技巧,FPGA/CPLD的設計思想與技巧是一個非常大的話題,本文僅介紹一些常用的設計思想與技巧,包括乒乓球操作、串并轉換、流水線操作和數據接口的同步方法。希望本文能引起工程師們的注意,如果能有意識地利用這些原則指導日

- 關鍵字:

FPGA CPLD 設計技巧

- FPGA/EPLD的自上而下設計方法,FPGA/EPLD的自上而下(Top-Down)設計方法: 傳統的設計手段是采用原理圖輸入的方式進行的,如圖1所示。通過調用FPGA/EPLD廠商所提供的相應物理元件庫,在電路原理圖中繪制所設計的系統,然后通過網表轉換產生某一特

- 關鍵字:

FPGA EPLD 自上而下 設計方法

- FPGA技術、低成本光學器件以及無源架構都為無源光網絡(PON)以及這些網絡的演進做出了巨大貢獻。系統級OEM廠商不斷發現,FPGA能夠提供技術性設計和經濟

- 關鍵字:

FPGA PON 無源光網絡

- 傳說中有一對美麗的紅舞鞋,穿上它,你將舞出最美麗的舞步…… 正式從事電子硬件設計工作有十幾年時光了,回憶起剛接觸電子,感觸很多……雖然經歷了很多酸甜苦辣,但也給我的生活增添了很多色彩…… 第一次真正意義上的接觸電子應當算是高中的時候。當時很喜歡學校圖書館里的一份雜志,雜志名字不記得了,只記得雜志里有兩頁是關于電子制作的,當時那兩頁一直是我的最愛……慢慢的積累了一些電子方面的知識,也逐漸有了自己要做一塊電路板的想法…… 那時我對電子的感情用“癡迷”兩個字來形容絕不為過――因這家境不好,我每月只有不

- 關鍵字:

ARM FPGA

- NI LabVIEW FPGA模塊可以幫助您利用LabVIEW程序框圖對一個FPGA進行編程。在其底層,該模塊采用代碼生成技術實現圖形化開發環境與FPGA硬件的整合。這種

- 關鍵字:

FPGA LabVIEW FlexRIO 模塊

- FPGA 解決方案和標準控制器內核比較, MicroBlaze處理器是賽靈思(Xilinx)在嵌入式開發套件 (EDK) 中提供的兩款32位內核之一,是實現硬件加速的靈活工具。圖1是MicroBlaze的典型設計。該內核含有一個32位乘法器,但不含浮點單元(FPU)、桶式移位器或專用硬

- 關鍵字:

FPGA 方案 標準 比較

fpga+mpu+mcu介紹

您好,目前還沒有人創建詞條fpga+mpu+mcu!

歡迎您創建該詞條,闡述對fpga+mpu+mcu的理解,并與今后在此搜索fpga+mpu+mcu的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473