epld 文章 最新資訊

FPGA/EPLD的自上而下設(shè)計(jì)方法

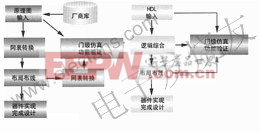

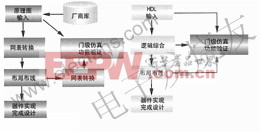

- FPGA/EPLD的自上而下設(shè)計(jì)方法,FPGA/EPLD的自上而下(Top-Down)設(shè)計(jì)方法: 傳統(tǒng)的設(shè)計(jì)手段是采用原理圖輸入的方式進(jìn)行的,如圖1所示。通過調(diào)用FPGA/EPLD廠商所提供的相應(yīng)物理元件庫,在電路原理圖中繪制所設(shè)計(jì)的系統(tǒng),然后通過網(wǎng)表轉(zhuǎn)換產(chǎn)生某一特

- 關(guān)鍵字: FPGA EPLD 自上而下 設(shè)計(jì)方法

FPGA/EPLD的自上而下設(shè)計(jì)方法

- FPGA/EPLD的自上而下設(shè)計(jì)方法,FPGA/EPLD的自上而下(Top-Down)設(shè)計(jì)方法: 傳統(tǒng)的設(shè)計(jì)手段是采用原理圖輸入的方式進(jìn)行的,如圖1所示。通過調(diào)用FPGA/EPLD廠商所提供的相應(yīng)物理元件庫,在電路原理圖中繪制所設(shè)計(jì)的系統(tǒng),然后通過網(wǎng)表轉(zhuǎn)換產(chǎn)生某一特

- 關(guān)鍵字: 方法 設(shè)計(jì) 自上而下 FPGA/EPLD

數(shù)話同傳控制器的設(shè)計(jì)與實(shí)現(xiàn)

- 話音和數(shù)據(jù)同傳有多種方案,這些方案大都先將話音信號(hào)數(shù)字化,經(jīng)過壓縮后與外部數(shù)據(jù)一起打包傳輸。主要區(qū)別在于發(fā)送一包話音數(shù)據(jù)與外部數(shù)據(jù)的占用時(shí)間,以及話音數(shù)據(jù)與外部數(shù)據(jù)在包內(nèi)的分割時(shí)長(zhǎng)。常見的有兩種方案[1

- 關(guān)鍵字: 實(shí)現(xiàn) 設(shè)計(jì) 控制器 同傳 數(shù)話同傳 EPLD AMBE話音 Codec GMSK Modem

基于EPLD技術(shù)的PCI總線接口設(shè)計(jì)

- PCI總線自其問世以來,以其諸多優(yōu)點(diǎn),在當(dāng)今的計(jì)算機(jī)系統(tǒng)中得到了廣泛應(yīng)用,已經(jīng)成為計(jì)算機(jī)設(shè)備的標(biāo)準(zhǔn)接口。本文在認(rèn)真分析PCI總線的接口信號(hào)和接口時(shí)序的基礎(chǔ)上,利用EPLD器件設(shè)計(jì)實(shí)現(xiàn)了PCI總線接口。由于EPLD器件支

- 關(guān)鍵字: EPLD PCI 總線 接口設(shè)計(jì)

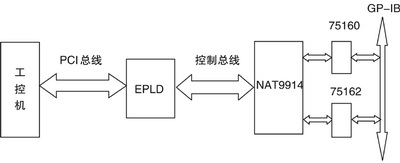

基于PCI總線的GP-IB接口電路設(shè)計(jì)

- 主要介紹作為從設(shè)備如何根據(jù)PCI總線協(xié)議設(shè)計(jì)PCI總線接口電路,從而實(shí)現(xiàn)基于PCI總線的GP-IB接口電路設(shè)計(jì),重點(diǎn)闡述PCI總線接口狀態(tài)機(jī)的設(shè)計(jì)。

- 關(guān)鍵字: PCI 狀態(tài)機(jī) GP-IB EPLD 200806

用EPLD實(shí)現(xiàn)單脈沖二次雷達(dá)的應(yīng)答解碼處理

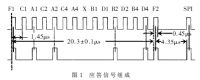

- 摘 要:用EPLD實(shí)現(xiàn)的單脈沖二次雷達(dá)應(yīng)答處理器。其主要功能包括:應(yīng)答框架脈沖檢測(cè),應(yīng)答信息解碼,將應(yīng)答信息裝配成飛機(jī)的同步應(yīng)答組形成目標(biāo)報(bào)告,丟棄非同步虛假應(yīng)答。 關(guān)鍵詞:?jiǎn)蚊}沖二次雷達(dá)? 應(yīng)答模式? EPLD 1 一次雷達(dá)與二次雷達(dá) 二次雷達(dá)與一次雷達(dá)基本上是并行發(fā)展的。與一次雷達(dá)相比,二次雷達(dá)有回波強(qiáng)、無目標(biāo)閃爍效應(yīng)、詢問波長(zhǎng)與應(yīng)答波長(zhǎng)不等的特點(diǎn),從而消除了地物雜波和氣象雜波的干擾。單脈沖技術(shù)應(yīng)用于二次雷達(dá),可以方便地基于多個(gè)波束對(duì)目標(biāo)測(cè)量,進(jìn)而有效地增加數(shù)

- 關(guān)鍵字: EPLD 單脈沖二次雷達(dá) 應(yīng)答模式

| 共11條 1/1 1 |

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司