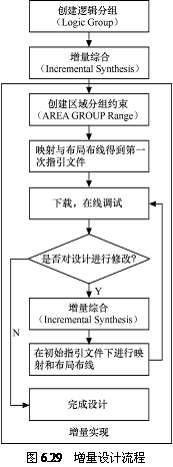

6.6 增量式設計(Incremental Design)技巧

本節將對ISE下增量式設計做一個全面的介紹。FPGA作為一種現場可編程邏輯器件,其現場可重編程特性能夠提高調試速度。每次硬件工程師可以很方便地改變設計,重新進行綜合、實現、布局布線,并對整個設計重新編程。

然而當設計算法比較復雜時,每一次綜合、實現、布局布線需要花很長的時間。即使僅僅改變設計中的一點,也會使綜合編譯的時間成倍增加。而且更為麻煩的是如果整個工程的運行頻率很高,對時序的要求也很嚴格,這樣重新布線往往會造成整個時序錯

關鍵字:

FPGA ISE

6.5 編譯與仿真設計工程

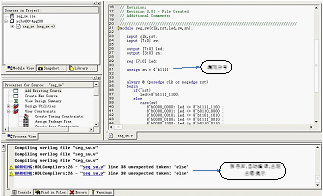

編寫代碼完成之后,一個很重要的工作就是驗證代碼功能的正確性,這就需要對代碼進行編譯與仿真。編譯主要是為了檢查代碼是否存在語法錯誤,仿真主要為了驗證代碼實現的功能是否正確。

編譯和仿真設計工程在整個設計中占有很重要的地位。因為代碼功能不正確或代碼的編寫風格不好對后期的設計會有很大的影響,所以需要花很多時間在設計工程的仿真上。

在這一節中將通過一個具體的實例來介紹如何對編譯工程代碼以及如何使用ISE自帶的仿真工具ISE Simulator進行仿真。

1.

關鍵字:

FPGA ISE

6.4 創建設計工程

本節將重點講述如何在ISE下創建一個新的工程。要完成一個設計,第一步要做的就是新建一個工程。具體創建一個工程有以下幾個步驟。

(1)打開Project Navigator,啟動ISE集成環境。

ISE的啟動請參見6.2節。

(2)選擇“File”/“New Project”菜單項,啟動新建工程對話框。

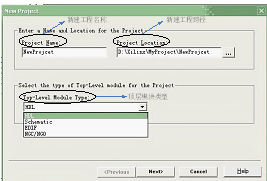

會彈出如圖6.9的對話框。

如圖6.9所示,新建工程時需要設置工程名稱和新建工程的路徑,還要設置

關鍵字:

FPGA ISE

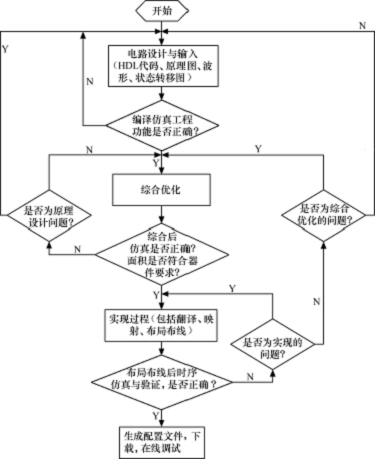

6.3 ISE軟件的設計流程

Xilinx公司的ISE軟件是一套用以開發Xilinx公司的FPGA&CPLD的集成開發軟件,它提供給用戶一個從設計輸入到綜合、布線、仿真、下載的全套解決方案,并很方便地同其他EDA工具接口。

其中,原理圖輸入用的是第三方軟件ECS;狀態圖輸入用的是StateCAD;HDL綜合可以使用Xilinx公司開發的XST、Synopsys公司開發的FPGA Express和Synplicity公司的Synplify/Synplify Pro等;測試激勵可以是圖

關鍵字:

FPGA Xilinx ISE

6.2 ISE軟件的安裝與啟動

6.2.1 ISE軟件的安裝

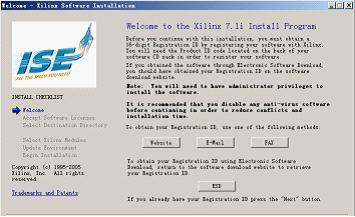

ISE的安裝改變了license管理方式,在安裝后并不需要任何license支持,僅僅是在這安裝過程式中輸入ISE的注冊序列號(Register ID)即可。ISE 7.1i安裝啟動界面如圖6.1所示。

圖6.1 ISE 7.1i安裝啟動界面

安裝ISE時只需要根據所選的版本是在PC機或工作站上,然后根據軟件的提示安裝即可,這里不做詳細敘述,只對安裝的幾個問題進行說明。

1.環境變量

關鍵字:

FPGA ISE

ISE軟件簡介

Xilinx作為當界上最大的FPGA/CPLD生產商之一,長期以來一直推動著FPGA/CPLD技術的發展。其開發的軟件也不斷升級換代,由早期的Foundation系列逐步發展到目前的ISE 9.x系列。

ISE是集成綜合環境的縮寫,它是Xillinx FPGA/CPLD的綜合性集成設計平臺,該平臺集成了設計、輸入、仿真、邏輯綜合、布局布線與實現、時序分板、芯片下載與配置、功率分析等幾乎所有設計流程所需工具。

ISE系列軟件分為4個系列:WebPACK、BaseX、Fo

關鍵字:

FPGA ISE

摘要

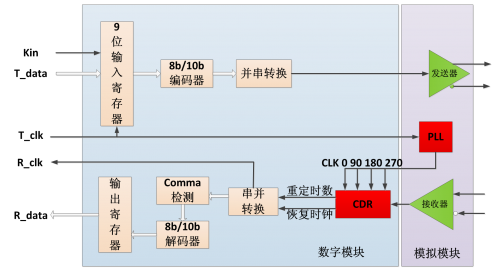

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立的ASSP 或ASIC 器件。在過去幾年中已經看到有內置SERDES 的FPGA 器件系列,但多見于高端FPGA芯片中,而且價格昂貴。

本方案是以CME最新的低功耗系列FPGA的HR03為平臺,實現8/10b的SerDes接口,包括SERDES收發單元,通過完全數字化的方法實現SERDES的CD

關鍵字:

京微雅格 FPGA

記得在上幾篇博客中,有幾名網友提出要加進去錯誤分析這一部分,那我們就從今天這篇文章開始加進去我在消化這段代碼的過程中遇到的迷惑,與大家分享。

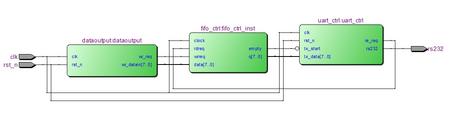

今天要寫的是一段基于FIFO的串口發送機設計,之前也寫過串口發送的電路,這次寫的與上次的有幾分類似。這段代碼也是我看過別人寫過的之后,消化一下再根據自己的理解寫出來的,下面是我寫這段代碼的全部流程和思路,希望對剛開始接觸的朋友來說有一點點的幫助,也希望有經驗的朋友給予寶貴的建議。

首先來解釋一下FIFO的含義,FIFO就是First Input Fi

關鍵字:

FPGA FIFO

1. 超安全SmartFusion2? SoC FPGA和 IGLOO2? FPGA

美高森美的超安全SmartFusion2? SoC FPGA和 IGLOO2? FPGA器件,無論在器件、設計和系統層次上的安全特性都比其他領先FPGA制造商更先進。新的數據安全特性現已成為美高森美主流SmartFusion2 SoC FPGA和 IGLOO2 FPGA器件的一部分,可讓開發人員充分利用器件本身所具有的同級別器件中的最低功耗,高可靠性和最佳安全技術,以期構建高度差

關鍵字:

美高森美 SmartFusion2 FPGA

本文介紹達芬奇技術的解讀文獻及應用案例,供大家參考。

解讀達芬奇技術

達芬奇技術是一種數字圖像、視頻、語音、音頻信號處理的新平臺,一經推出,就受到熱烈歡迎,以其為基礎的應用開發層出不窮。該技術是一種內涵豐富的綜合體,包含達芬奇處理器、軟件、開發環境、算法庫和其他技術支持等。正因為涉及的技術面廣,因此有比較高的技術門檻。

視頻跟蹤算法在Davinci SOC上的實現與優化

本文在基于雙核DM6446的系統平臺上,利用改進后的跟蹤算法實現了智能目標跟蹤系統。該算法可以成功跟蹤目標,

關鍵字:

DSP ARM DM6446

引言

本文采用ARM+DSP雙核架構的OMAP3530系列的處理器,道路圖像處理部分由支持浮點運算的DSP核來完成,圖像采集工作和系統的控制工作由ARM核來完成,這樣的作業分配提高了系統的實時性、集成性和可靠性。

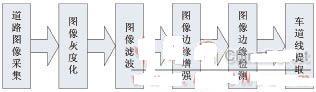

車道線識別算法研究

本文提出的車道線識別算法的流程如下圖1所示,首先通過OV7670攝像頭捕獲道路圖像,然后按照流程圖中的步驟處理圖像,最后得到清晰的車道標志線,為以后智能車輛路徑規劃和避障提供支持。

道路圖像灰度化

圖像灰度變換是對圖像像素進行拉伸,從而擴大圖

關鍵字:

OMAP3530 ARM OV7670

自上個世紀80年代起,微軟和英特爾為推動PC產業的發展,組成了所謂的Wintel聯盟,即兩家公司在PC產業內密切合作,以推動Windows操作系統在基于英特爾CPU的PC機上運行,掌握著計算機行業的大權。然而近年來,隨著移動互聯網的發展,Wintel聯盟逐漸成為過去式。但去年下半年,Windows平板在國內的銷量出現幾何級成長,微軟和英特爾同時發力,Wintel聯盟大有卷土重來之勢。

關鍵字:

Wintel ARM 微軟

對自己的設計的實現方式越了解,對自己的設計的時序要求越了解,對目標器件的資源分布和結構越了解,對EDA工具執行約束的效果越了解,那么對設計的時序約束目標就會越清晰,相應地,設計的時序收斂過程就會更可控。

下文總結了幾種進行時序約束的方法。按照從易到難的順序排列如下:

0.核心頻率約束

這是最基本的,所以標號為0.

1.核心頻率約束+時序例外約束

時序例外約束包括FalsePath、MulticyclePath、MaxDelay、MinDelay.但這還不是最完整的時序約束

關鍵字:

FPGA 時序約束

FPGA采用了邏輯單元陣列概念,內部包括可配置邏輯模塊、輸出輸入模塊和內部連線三個部分。每一塊FPGA芯片都是由有限多個帶有可編程連接的預定義源組成來實現一種可重構數字電路。

長久以來新型FPGA的功能和性能已經為它們贏得系統中的核心位置,成為許多產品的主要數據處理引擎。

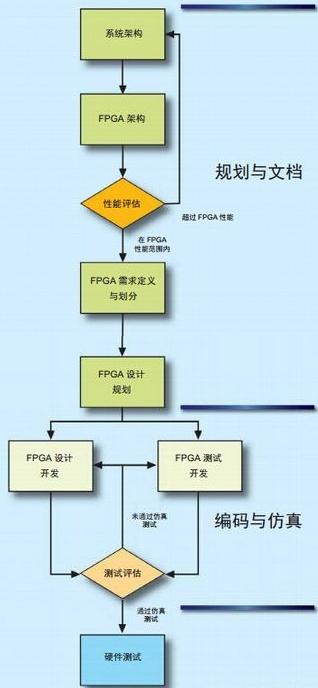

鑒于FPGA在如此多應用中的重要地位,采取正式且注重方法的開發流程來處理FPGA設計比以往更加重要。該流程旨在避免開發周期后期因發現設計缺陷而不得不進行費時費錢的設計修改,而且該缺陷還可能對項目進度計劃、成本和質量造成災

關鍵字:

FPGA

按照基于Windows的語言(C、C++、C#)等編程語言的初學入門教程,第一個歷程應該是“Hello World!”的例程。但由于硬件上的驅動難易程度,此例程將在在后續章程中推出。硬件工程師學習開發板的第一個例程:流水燈,一切美好的開始。

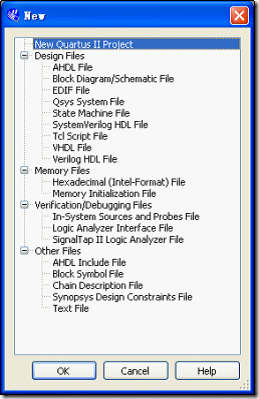

本章將會在設計代碼的同時,講解Quartus II 軟件的使用,后續章節中只講軟件的思想,以及解決方案,不再做過多的累贅描述。

一、Step By Step 建立第一個工程

(1)建立第一個工程,File-New-New

關鍵字:

FPGA Quartus II

fpga+arm介紹

您好,目前還沒有人創建詞條fpga+arm!

歡迎您創建該詞條,闡述對fpga+arm的理解,并與今后在此搜索fpga+arm的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473