【從零開始走進FPGA】美好開始——我流啊流啊流

按照基于Windows的語言(C、C++、C#)等編程語言的初學入門教程,第一個歷程應該是“Hello World!”的例程。但由于硬件上的驅動難易程度,此例程將在在后續章程中推出。硬件工程師學習開發板的第一個例程:流水燈,一切美好的開始。

本文引用地址:http://www.104case.com/article/268641.htm本章將會在設計代碼的同時,講解Quartus II 軟件的使用,后續章節中只講軟件的思想,以及解決方案,不再做過多的累贅描述。

一、Step By Step 建立第一個工程

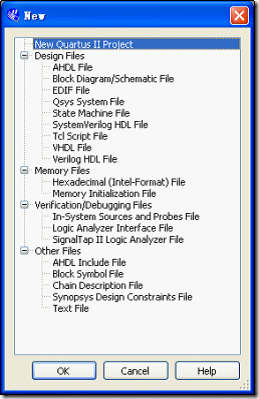

(1)建立第一個工程,File-New-New Quartus II Project,如下圖所示,OK。

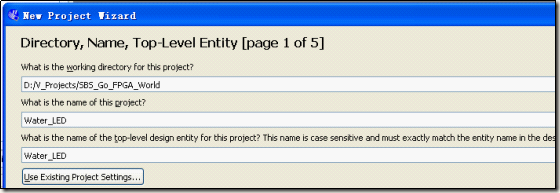

(2)Next,如下圖所示,選擇工程目錄(不能有空格,中文路徑),同時輸入工程名與頂層文件名。

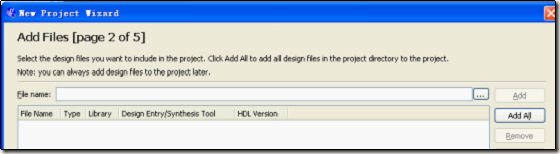

(3)若有現成的代碼,可以直接選擇添加入工程;否則,直接next,進入下一步,如下圖所示:

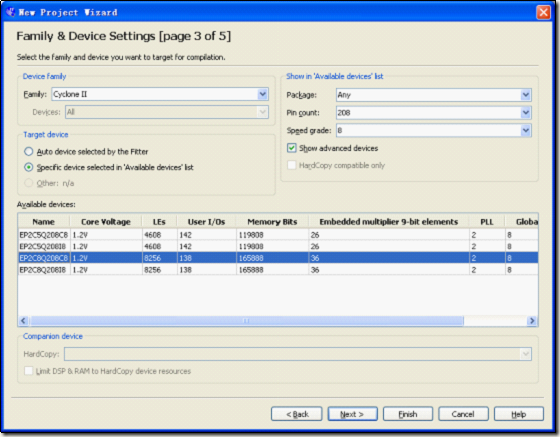

(4)根據自己的硬件設施,選擇相應的設備目標器件。

(5)Next,Finish。

二、工程代碼設計

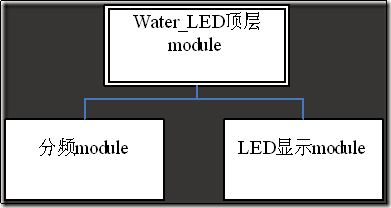

1. water_led_design工程文件結構:

如上圖所示,工程分為三個模塊,分別為:

(1)頂層模塊 : 例化各個模塊,工程的最高級別文件。

(2)分頻模塊 : 通過分頻得到固定的頻率(10Hz)。

(3)LED顯示模塊: 隨固定頻率,來操作LED燈。

2. 代碼設計

(1)warter_led.v模塊設計

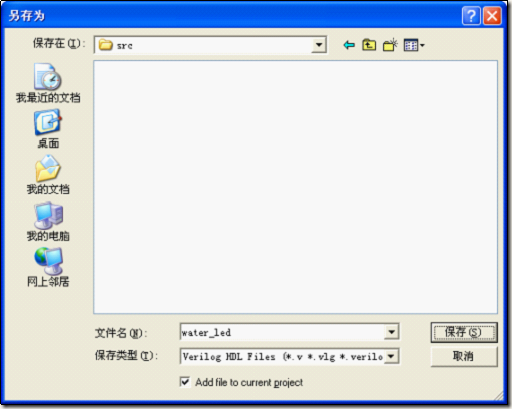

a) New-File,新建verilog文件,保存于新建在工程目錄下的src文件夾中(只是為了工程文件結構組織的清晰,更善于管理)。如下圖所示:

b) 輸入代碼,定義輸入輸出接口,如下所示:

module water_led

(

input clk, //global clock 50MHz

input rst_n, //global clock reset

output [5:0] led_data //user led interface

);

endmodule

fpga相關文章:fpga是什么

c++相關文章:c++教程

評論