- 業界首款支持免專利費RISC-V開放式指令集架構(ISA)的SoC現場可編程門陣列(FPGA)近日開始量產,迎來嵌入式處理器發展歷程中的一個重要里程碑。隨著客戶繼續快速采用PolarFire? SoC FPGA,Microchip Technology Inc.(美國微芯科技公司)宣布MPFS250T以及之前發布的MPFS025T已具備量產條件。Microchip同時宣布,旗下Mi-V生態系統將繼續簡化RISC-V的采用,以支持新一類體積更小、功耗和成本更低的工業、物聯網和其他邊緣計算產品。Microch

- 關鍵字:

RISC-V FPGA

- 目錄???第一節?| ???摘要?P3?第二節?| ???DC-SCM是什么??P3?第三節?|??? 為什么要使用DC-SCM??P3?第四節?|?? ?DC-SCM架構?P4?第五節?| ???D

- 關鍵字:

FPGA DC-SCM

- 方案描述:本方案描述了Xilinx FPGA在汽車倒車顯示上的應用。系統采用I2C實現對CMOS Sensor的控制,將采集的數據進行校正,陰影移除,縮放后通過TFT顯示出來。使用Picoblaze實現對系統的靈活控制和算法運用,外掛SDRAM或Flash對圖像進行存儲。方案設計圖:方案關鍵器件表:

- 關鍵字:

Xilinx FPGA 汽車電子

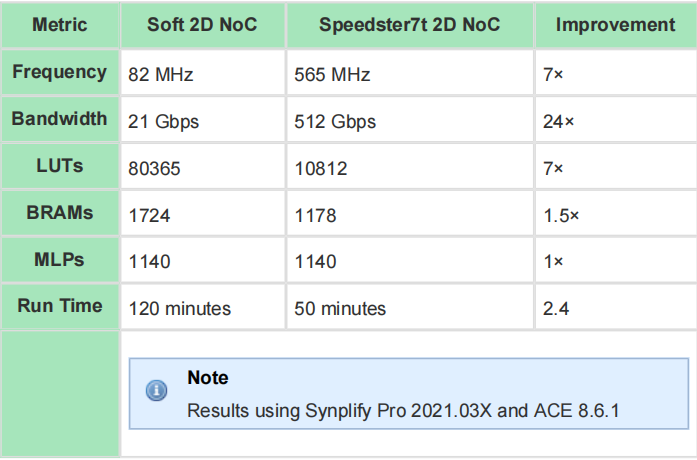

- 摘要隨著旨在解決現代算法加速工作負載的設備越來越多,就必須能夠在高速接口之間和整個器件中有效地移動高帶寬數據流。Achronix的Speedster?7t獨立FPGA芯片可以通過集成全新的、高度創新的二維片上網絡(2D NoC)來處理這些高帶寬數據流。Achronix的FPGA中特有的2D NoC實現是一種創新,它與用可編程邏輯資源來實現2D NoC的傳統方法相比,有哪些創新和價值呢?本白皮書討論了這兩種實現2D NoC的方法,并提供了一個示例設計,以展示與軟2D NoC實現相比,Achronix 2D

- 關鍵字:

Achronix FPGA 2D NoC

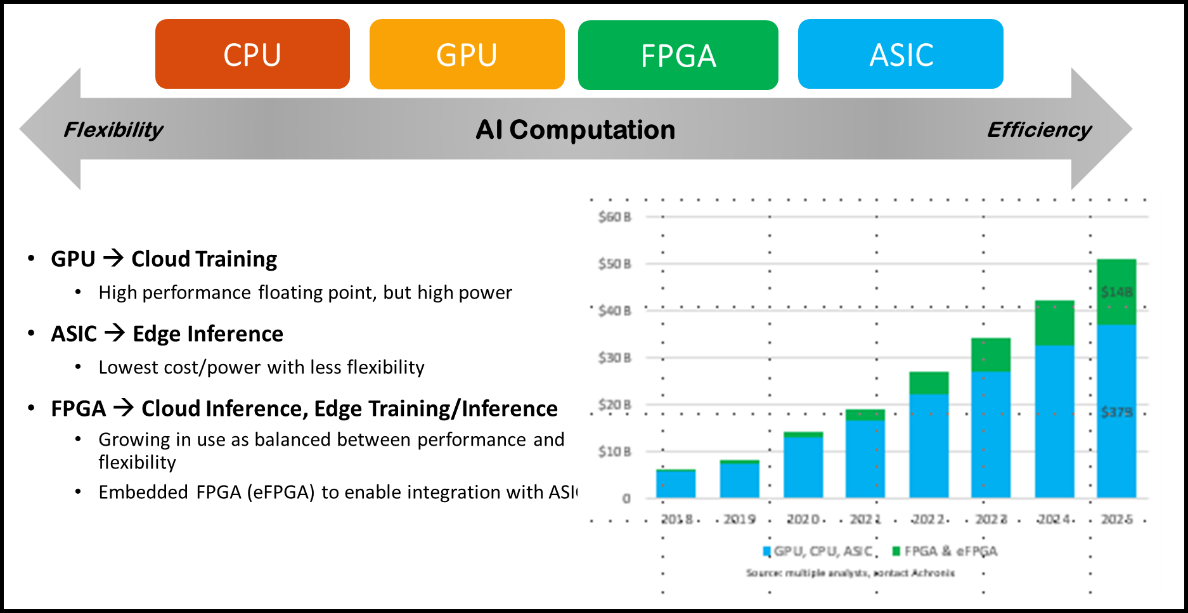

- 四大類人工智能芯片(GPU、ASIC、FGPA、類腦芯片)及系統級智能芯片在國內的發展進度層次不齊。用于云端的訓練、推斷等大算力通用 芯片發展較為落后;適用于更多垂直行業的終端應用芯片如自動駕駛、智能安防、機器人等專用芯片發展較快。超過80%中國人工智能產業鏈企 業也集中在應用層。?總體來看,人工智能芯片的發展仍需基礎科學積累和沉淀,因此,產學研融合不失為一種有效的途徑。研究主體界定:面向人工智能領域的芯片及其技術、算法與應用無芯片不AI , 以AI芯片為載體實現的算力是人工智能發展水平的重要衡

- 關鍵字:

AI芯片 GPU ASIC FPGA 行業研究

- 高性能現場可編程邏輯門陣列(FPGA)和嵌入式FPGA(eFPGA)半導體知識產權(IP)領域的領導性企業Achronix半導體公司宣布:公司已任命江柏漢先生為全球銷售副總裁。江先生為Achronix帶來了超過30年的半導體產品銷售經驗,并將領導Achronix全球銷售組織體系。在加入Achronix之前,江先生曾在Marvell半導體公司擔任銷售副總裁兼中國區總經理并常駐上海。在Marvell,江先生通過贏得一些戰略性的項目和提高市場份額,成功地加快了公司業務的增長,同時對多項收購和資產剝離進行了整合和

- 關鍵字:

Achronix FPGA

- 萊迪思半導體宣布其CrossLink-NX FPGA和專為AI優化的軟件解決方案,將用于聯想最新的ThinkPad X1系列筆記本電腦中。全新的聯想ThinkPad產品系列采用萊迪思充分整合的客戶端硬件和軟件解決方案,能夠在不損失效能或電池使用時間的情況下提供優化的使用者體驗,包括沉浸式互動、更好的隱私保護和更高效的協作。 萊迪思FPGA助力聯想新一代網絡邊緣AI體驗萊迪思營銷和業務發展副總裁Matt Dobrodziej表示:「我們的AI優化解決方案產品旨在滿足希望實現更高智能的各種網絡邊緣應

- 關鍵字:

萊迪思 FPGA 聯想 邊緣AI

- 針對固體火箭發動機推進劑藥柱應變量大、高頻振動時應變不易測量的問題,基于FPGA和柔性應變計設計了柔性應變測量裝置。柔性應變計的測量范圍大,可以測量雙向應變,解決了推進劑藥柱應變測量的難題。FPGA具有實時性高、并行運行的優點,解決了多路應變實時采集的難題。該應變測量裝置還可用于其他高分子材料的應變測量。

- 關鍵字:

推進劑 柔性應變計 FPGA 高頻振動 高速采集 202111

- 1? ?為什么AI/ML發展如此迅速?多年來,人工智能(AI)/機器學習(ML)市場一直以指數級的速度快速增長,其解決方案遍布我們周圍,從機器人和其他機械系統的預測故障算法、電子商務中的購買行為建議、自動駕駛車輛的目標檢測、電子交易中的風險緩解到DNA測序等等,我們身邊有各種各樣的解決方案,示例不勝枚舉。那么,為什么AI/ML發展如此迅速呢?據IDC、Gartner和其他市調機構的分析,全球大約80%的數據是非結構化數據。電子郵件、照片、語音郵件、視頻和許多其他數據源每天都在堆積。無論

- 關鍵字:

AI 機器學習 FPGA

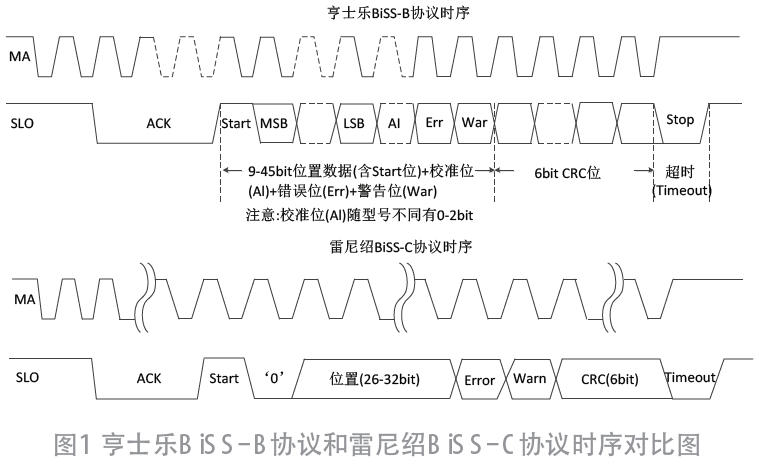

- BiSS協議是一種高速同步串行通信協議,使用BiSS協議的編碼器有利于提高伺服控制系統的動態性能,在高精度絕對式編碼器中應用廣泛。本文在分析BiSS協議數據幀特點的基礎上,利用FPGA設計了BiSS協議編碼器解碼器,采集了BiSS協議編碼器位置數據和總線波形,通過與DSP聯合使用,基于BiSS協議編碼器對永磁同步電機的動態性能進行了驗證,結果表明該設計的合理性。

- 關鍵字:

BiSS FPGA 編碼器 DSP 202108

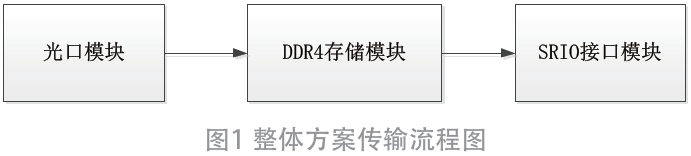

- 5G通信的主要特征包括“高速率、大帶寬”,為了滿足高速率、大帶寬數據的傳輸要求,需要一種存儲技術對數據進行存儲。本文就存儲技術結合DDR4協議,設計了一種DDR4傳輸機制,本研究采用高性能的XCVU9P系列的FPGA芯片作為控制芯片,使用其內部自帶的DDR4 SDRAM(MIG)IP核進行例化核設計。經過驗證,實現在250 MHz時鐘下對DDR4 SDRAM的讀/寫操作,數據無丟失,能夠保證高速率、大帶寬數據正常傳輸,該傳輸機制具有良好的可靠性、適用性及有效性。

- 關鍵字:

DDR4 高速率 大帶寬 FPGA 202108

- 針對5G毫米波通信宏基站、微基站等設備的研發、生產、預認證、維修保障等測試需求,設計一款可應用于“5G新基建”通信設備產業鏈多環節所需儀表的高效多速率信號接收機處理模塊。采用先進的并行多相濾波技術和任意速率比FFT處理技術,基于FPGA算法平臺實現毫米波5G接收機多路信號接收時域/頻域并行變速率處理邏輯電路,提高5G復雜波形接收機信號解析的實時性。實驗結果表明,該電路能高效完成5G復雜波形接收機信號的時域/頻域解析,適合作為毫米波5G接收機多速率數據處理實施方案,滿足毫米波5G接收機的功能設計要求。

- 關鍵字:

FPGA 5G 毫米波 接收機 202105

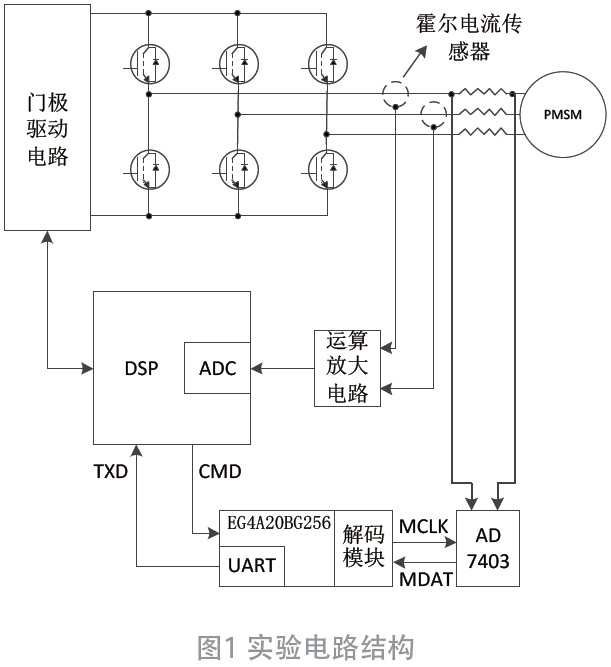

- AD7403是一種Σ-Δ型模數轉換器,廣泛應用于需要電氣隔離的伺服控制電機相電流采集場合。EG4A20BG256是一種國產FPGA,適用于伺服控制系統信號采集﹑接口擴展等應用場景。本文基于EG4A20BG256 FPGA設計了AD7403模數轉換器接口電路,采集永磁同步電機相電流,并與伺服控制電路內霍爾電流傳感器和DSP采樣結果進行了對比。結果表明,EG4A20BG256 FPGA可以通過AD7403模數轉換器實現對永磁同步電機相電流的準確采集。

- 關鍵字:

AD7403 EG4A20BG256 FPGA DSP 永磁同步電機 202105

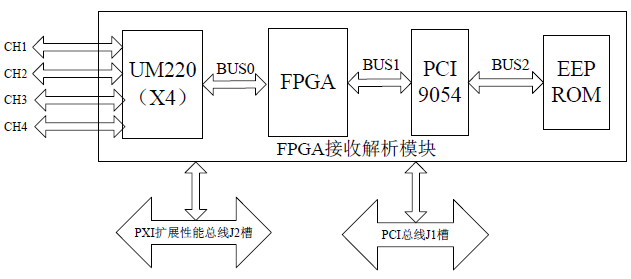

- 設計并實現了一種BD/GPS衛星導航信號多通道隔離轉換測量顯示系統。該系統將一路輸入的BD/GPS信號通過功分器轉換為等量的四路隔離輸出信號,經FPGA解析后實時顯示在電腦屏幕上,為BD/GPS信號的使用提供直觀的數據基礎。

- 關鍵字:

BD/GPS FPGA 功分器 隔離 202107

fpga)介紹

您好,目前還沒有人創建詞條fpga)!

歡迎您創建該詞條,闡述對fpga)的理解,并與今后在此搜索fpga)的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473