- 基于FPGA的數字電視信號發生器的設計與實現,電視信號的數字化使得數字電視設備越來越受到廣大電子消費者的青睞,如何選擇自己理想的數字電視產品,也成了消費者關心的問題,評價、測試電視系統與設備運行的質量狀況成為廣播電視行業所關注的熱點。而數字電視信號發生器能提供可視的測試圖像信號,直觀、快捷的測試方法,因此,數字電視信號發生器成為目前電子設計的熱門研究課題,他在數字電視節目制作播出、科研、生產以及售后服務過程中起著不可或缺的作用。本文設計了一種基于FPGA的數字電視信號友生器,該信號發生器以一種單芯片多配置

- 關鍵字:

設計 實現 信號發生器 數字電視 FPGA 基于

- 惠瑞捷半導體科技有限公司推出Inovys™硅片調試解決方案,以滿足更高效調試的需求,加速新的系統級芯片 (SoC)器件的批量生產。惠瑞捷全新的解決方案把革命性的Inovys FaultInsyte 軟件和具有可擴充性和靈活性惠瑞捷V93000 SoC測試系統結合在一起。這是一款集成式解決方案,通過把電路故障與復雜的系統級芯片上的物理缺陷對應起來,可以大大縮短錯誤檢測和診斷所需的時間。它明顯地縮短了制造商采用90 nm(及以下)工藝調試、投產和大批量生產所需的時間。

由于復雜的系統級芯

- 關鍵字:

半導體 惠瑞捷 硅片調試 SoC

- picoChip今日宣布推出特別針對快速增長的家用基站市場的新型SoC基帶處理器PC3xx系列,該系列新一代器件結合了picoChip經過現場驗證的modem軟件,使家用基站制造商在提高性能的同時充分降低BOM成本。這一成本節省對大批量消費類家用基站部署而言是一個關鍵推動力量。

picoChip PC302是該新系列的第一個成員,它是一個符合TR25.820標準的HSPA家用基站單片解決方案,并集成了最近成為標準的Iu-h接口。PC302支持高達4個用戶的家用基站和中小企業(SME)接入點,以及

- 關鍵字:

picoChip 家用基站 SoC 基帶 處理器

- 基于現場可編程門陣列 (FPGA) 核心的實施體現了先進的現代航空電子設計方法。

這項技術具有多種優勢,如廢棄組件管理、降低設計風險、提高集成度、減小體積、降低功耗和提高故障平均間隔 時間(MTBF)等,吸引著用戶將原來的系統轉移到此項技術。MIL-STD-1553 的市場可能隨著這種趨勢而繁榮起來 ;事實上,某些客戶已經覺得這項技術的實施有點姍姍來遲。

MIL-STD-1553 核心帶來了多種好處,它代表著徹底告別了 ASIC 傳統。FPGA 中加入一項知識產權核心,就獲得了一種與眾不同

- 關鍵字:

FPGA 航空電子 ASIC MIL-STD-1553

- 互聯網的繁榮和無線通訊及存儲行業的發展使得實時數據通訊量成指數級增長。數據通訊量的急劇增加使系統可用性顯得更加關鍵,因為系統即使停一秒鐘也意味著將產生巨大的影響,并將減少運營商的收入。為了使系統的宕機時間為零,可以將系統設計成可熱插拔的形式。熱插拔是指系統在正常運行時可以從背板上插入或取出電路板,而不會對主系統的正常工作產生影響。熱插拔也稱為熱切換(hot swap)或熱插入。

快速發展的半導體工藝技術使支持熱插拔的設計更趨復雜,因為工藝尺寸越來越小,IC的工作電壓也越來越低,而且不同的I/O標

- 關鍵字:

PLD 熱插拔 加電順序保護 FPGA

- Altera公司宣布,開始提供基于FPGA/Intel? Xeon?處理器的前端總線(FSB)模塊。采用了多片Altera? Stratix? III FPGA,并且使用Intel QuickAssist技術,XtremeData XD2000i In-Socket加速器(ISA)展示了1066 MHz協處理解決方案。

?

XD2000i系列在目前市場上最小封裝中提供密度最大的Stratix III FPGA。模塊使用三片FPGA,一片用于基于Inte

- 關鍵字:

FPGA XtremeData Intel FSB

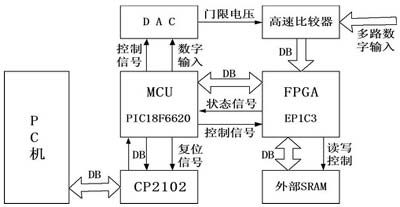

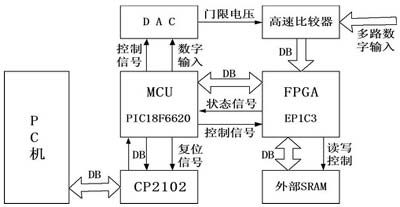

- 基于FPGA的USB2.0高速、低成本的虛擬邏輯分析儀的設計原理與實現方法。重點介紹了邏輯分析儀的觸發方式設計以及利用CP2102芯片構建USB接口、實現系統與PC通信的方法。

關鍵詞:虛擬邏輯分析儀;FPGA;觸發設計;USB2.0;CP2102

引言

傳統的邏輯分析儀體積龐大、價格昂貴、通道數目有限,并且在數據采集、傳輸、存儲、顯示等方面

- 關鍵字:

FPGA USB2.0 虛擬邏輯分析儀 數據采集 Altera

- 語音激活檢測VAD(Voice Activity Detection)是一種通過特定的判決準則判斷語音中出現的停頓和靜默間隔,檢測出有效語音部分的技術。運用這種技術可以在確保語音質量的前提下,對不同類別的語音段采用不同的比特數進行編碼,從而降低語音的編碼速率。由于在雙工移動通信系統中,一方只有35%的時間處于激活狀態[1],如何降低靜音期的編碼速率對于減少傳輸帶寬、功率以及容量具有積極的作用,因此VAD技術在語音通信領域具有重要的使用價值。隨著適合于變比特率語音編碼的CDMA和PRMA等多址技術的出現

- 關鍵字:

FPGA VAD 短時能量 短時過零率 FIFO 濾波器

- 音視頻軟件供應商SPIRIT公司和Tensilica公司今日宣布雙方結成戰略伙伴關系,并發布18個經過優化的高質量數字音頻和語音算法軟件包,可支持SOC設計中日益流行的HIFI2音頻引擎。

SPIRIT音頻軟件包現包括:AAC-LC 編解碼器、aacPlus v1及v2編解碼器、BSAC 解碼器、MP3編解碼器、Ogg Vorbis解碼器, 和WMA編解碼器。 語音編碼包括AMR-NB (窄帶)、AMR-WB和G.729AB。

此外,在戰略伙伴關系框架下,雙方將致力于在Tensilica公

- 關鍵字:

DSP Tensilica SPIRIT 移動多媒體 音視頻 SOC

- 賽靈思公司(Xilinx, Inc.)宣布推出一款集成了賽靈思汽車(XA)現場可編程門陣列(FPGA)和知識產權(IP)的解決方案。這一集成解決方案包括在針對汽車音響本體(head unit)應用的低功耗Intel車載信息娛樂(IVI)參考設計中。該參考設計結合了XA解決方案與Intel® Atom™ 處理器,為系統開發人員在開發開放式汽車信息娛樂平臺時提供了更高級別的性能、可擴展能力和靈活性。

與消費者在家庭和辦公室中的需求一樣,車載數字信息訪問和娛樂應用的需求也在不斷增長

- 關鍵字:

Xilinx 低功耗 Intel 車載信息娛樂 FPGA

- FPGA系統的供電要求和最新DC/DC穩壓器解決方案,隨著FPGA制造工藝尺寸持續縮小、設計配置更加靈活,以及采用FPGA的系統的不斷發展,原來只采用微處理器和ASIC的應用現在也可以用FPGA來實現了。最近FPGA供應商推出的新型可編程器件進一步縮小了FPGA和ASIC之間的性能差別。盡管這類器件的可配置性對設計工程師很有吸引力,但使用這些器件所涉及的復雜設計規則和接口協議,要求設計工程師經過全面的培訓,并需要進行參考設計評估、設計仿真和驗證工作。另一方面,FPGA應用中非常復雜的模擬設計,例如用于內核

- 關鍵字:

DC/DC 穩壓器 解決方案 最新 要求 系統 供電 FPGA

- 本報訊 北京大學出版社日前宣布,將出版由新思科技和ARM共同撰寫的先進的SoC(片上系統)設計功耗管理實用指南《低功耗設計方法學》的中文版。同時,北京大學還將基于《低功耗設計方法學》設置一套低功耗設計課程,并將其推廣至中國的其他各所大學。2007年8月發行的《低功耗設計方法學》英文版已經成為低功耗設計廣被采納的標準方法。

- 關鍵字:

北京大學 新思科技 ARM SoC

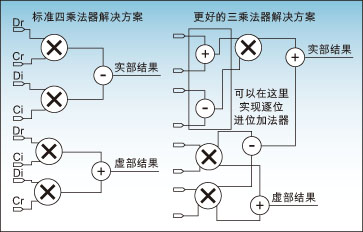

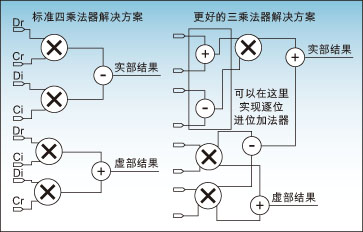

- 基于WiMax及其派生標準的新興寬帶無線協議需要越來越高的吞吐量和數據速率。這些協議提出的快速芯片速率和數字射頻處理可以在使用FPGA方案的硬件上得到最佳的實現。

FPGA非常適合作為高性能、高性價比的解決方案來實現這些物理層協議中的數字功能,因為它們包括以下豐富的資源:

1.DSP模塊,可以用來實現各種FIR濾波和FFT/IFFT操作所要求的乘法器和加法器/累加器功能;

2. SERDES收發器,可以支持無線前端與基帶數字板之間的CPRI和OBSAI接口;

3. 重要的FPG

- 關鍵字:

FPGA 乘法器 無線 基站 WiMax DSP IP核

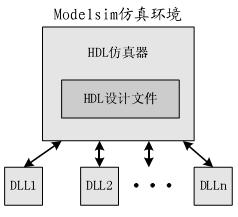

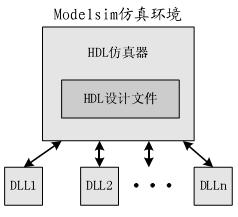

- 1、Modelsim 及 FLI接口介紹

Modelsim是 Model Technology(Mentor Graphics的子公司)的 HDL 硬件描述語言仿真軟件,可以實現 VHDL, Verilog,以及 VHDL-Verilog 混合設計的仿真。除此之外,Modelsim還能夠與 C 語言一起實現對 HDL 設計文件的協同仿真。同時,相對于大多數的 HDL 仿真軟件來說,Modelsim 在仿真速度上也有明顯優勢。這些特點使 Modelsim 越來越受到 EDA設計者、尤其是 FPGA

- 關鍵字:

FPGA 仿真 Modelsim FLI VHDL

fpga soc介紹

您好,目前還沒有人創建詞條fpga soc!

歡迎您創建該詞條,闡述對fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473