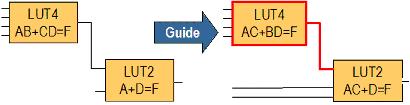

- 在FPGA環境下,設計保存實施比較復雜,需要保存的事項包括:一項設計的HDL描述、一個模塊的綜合網表、約束文件內的布局信息,以及在局部比特文件中的配置數據。賽靈思集成軟件環境(ISE) 9.1i 軟件以新的SmartCompile 技術為特色,其中包含兩種新的方法:SmartGuide和Partitions,這兩種方法可以保存像布局或布線這樣的設計執行數據,并且可以減少解決問題所花費的時間。

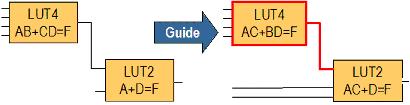

SmartGuide采用命名和拓樸匹配技術來識別一個FPGA設計中相對于以前的實現還沒有發生改變的各個部

- 關鍵字:

FPGA

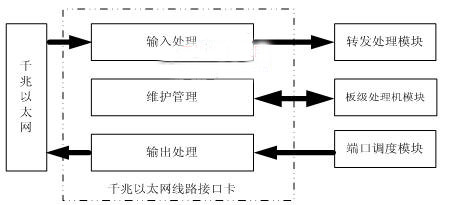

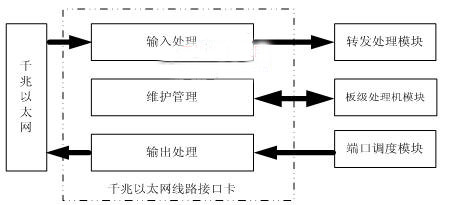

- 本文根據十接口千兆以太網線路接口卡設計的功能需求和性能需求,按照數據處理流程劃分功能模塊,以PM3388作為鏈路層處理芯片和兩片高性能FPGA作為鏈路層處理芯片完成了系統設計,并給出了具體實現方案。對兩片FPGA控制功能的實現做了重點闡述,對實現難點做了深入的分析。

1 前言

隨著網絡規模的持續膨脹和新型網絡應用需求的不斷增長,目前基于IPv4技術的因特網在可擴展性、IP地址空間、安全、服務質量控制、移動性、運營管理和盈利模式等諸多方面面臨著挑戰,尤其是地址空間匱乏、可擴展性差等缺陷嚴重制

- 關鍵字:

FPGA

- 您可以顯著提高無線系統中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結構的靈活性和目前受益于并行處理的FPGA架構中的嵌入式DSP模塊。

常見于無線應用中這類處理包括有限沖激響應(FIR)濾波、快速傅里葉變換(FFT)、數字上下變頻和前向誤差校正(FEC)。Xilinx? Virtex-4和Virtex-5架構提供多達512個并行嵌入式DSP乘法器,這些乘法器的工作頻率高于500MHz,最高可提供256 GMAC的DSP性能。

將需要高速并行處理的工作卸載給FPGA,而將需要高速

- 關鍵字:

FPGA

- 介紹了基于Altera公司FPGA的高速DMUX(數據分路器)設計。通過與DMUX專用器件的比較,說明了這種實現方式的優勢。

- 關鍵字:

FPGA DMUX

- ARM(Advanced RISC Machines)是微處理器行業的一家知名企業,設計了大量高性能、廉價、耗能低的RISC處理器、相關技術及軟 件。ARM架構是面向低預算市場設計的第一款RISC微處理器,基本是32位單片機的行業標準,它提供一系列內核、體系擴展、微處理器和系統芯片方案,四 個功能模塊可供生產廠商根據不同用戶的要求來配置生產。由于所有產品均采用一個通用的軟件體系,所以相同的軟件可在所有產品中運行。目前ARM在手持設備 市場占有90以上的份額,可以有效地縮短應用程序開發與測試的時間,也降低了

- 關鍵字:

ARM DSP FPGA 特點 區別

- 引言

傳統的邏輯分析儀體積龐大、價格昂貴、通道數目有限,并且在數據采集、傳輸、存儲、顯示等方面存在諸多限制,在很大程度上影響了其在實際中的應用。選用高性能的FPGA芯片進行數據處理,充分利用PC的強大處理功能,配合LabView圖形化語言開發的虛擬邏輯分析儀,其數據處理和傳輸速率大大提高,適用性極大增強,其顯示、操作界面和低廉的成本較之傳統的邏輯分析儀具有極大的優勢和發展前景。

工作原理

本設計選用Altera公司的Cyclone系列FPGA器件EP1C3進行數據采集和處理,外接SR

- 關鍵字:

FPGA

- 在電子產品中,鍵盤是最基本的輸入設備,然而在應用中都采用通用的鍵盤掃描器件是不現實的,需要單獨設計成專用的小鍵盤。現代EDA(電子設計自動化)技術提供了一種很好的途徑,利用VHDL硬件描述語言和FPGA器件可以很方便地構建鍵盤掃描模塊。經過實際操作檢驗,該模塊可以很好地對每一次按鍵動作進行掃描和響應,實現預先設計的功能。

1 概述

1.1 通用鍵盤和專用鍵盤

在現代個人計算機系統中,一般都采用通用的標準鍵盤(如:標準101/102鍵盤或Microsoft自然PS/2鍵盤)來實現人與計

- 關鍵字:

FPGA

- Altera公司今天宣布, 深圳邁瑞生物醫療電子股份有限公司授予Altera 2007年度“優秀供應商獎”,這是雙方長期互惠合作的結果。邁瑞公司位于中國深圳,是醫療設備開發、生產和營銷的龍頭公司。Altera是2007年邁瑞供應商大會上唯一獲得該獎項的FPGA供應商。

在年度供應商大會上,邁瑞公司表達了對最有價值合作伙伴的感謝,這些合作伙伴不斷開拓創新,提高了公司的效能。Altera提供的功能、價值和技術支持契合邁瑞公司的需求,得到了 邁瑞 的認可。

邁瑞公司采購部

- 關鍵字:

Altera FPGA

- PLD是可編程邏輯器件(Programable Logic Device)的簡稱,FPGA是現場可編程門陣列(Field Programable Gate Array)的簡稱,兩者的功能基本相同,只是實現原理略有不同,所以我們有時可以忽略這兩者的區別,統稱為可編程邏輯器件或PLD/FPGA。

PLD是電子設計領域中最具活力和發展前途的一項技術,它的影響絲毫不亞于70年代單片機的發明和使用。

PLD能做什么呢?可以毫不夸張的講,PLD能完成任何數字器件的功能,上至高性能CPU,下至簡單的74

- 關鍵字:

PLD FPGA 入門

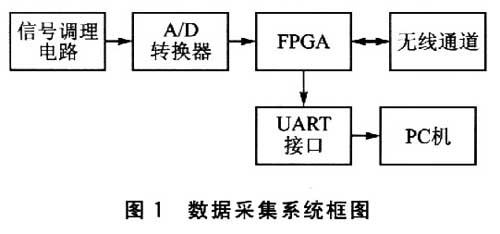

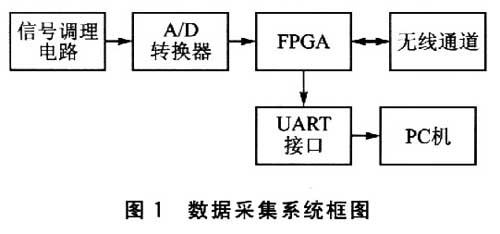

- 數據采集在工業測試系統中是一個很重要的環節,其精確性和可靠性是至關重要的。本文闡述的數據采集系統精度高達16位,能夠對8個外部模擬通道進行A/D采樣,最大模擬輸入信號范圍達到-15~+15V。該系統具有限幅保護功能,程序編寫簡便,能夠實現對遠端數據的采集和傳輸。

1 系統硬件設計

數據采集系統框圖如圖1所示。

?

圖中,A/D轉換器采用了TI公司的16位逐次逼近型ADS8344;FPGA主要用于控制ADC的啟動、停止和查詢ADC狀態等,同時對數據進行高速數據緩

- 關鍵字:

ADS8344 FPGA 數據采集

- 引 言

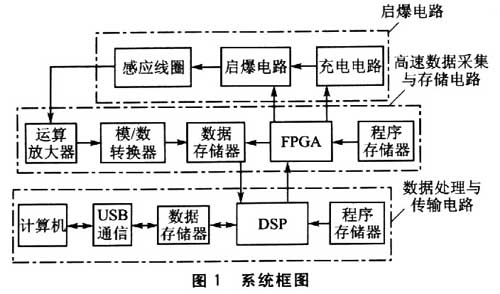

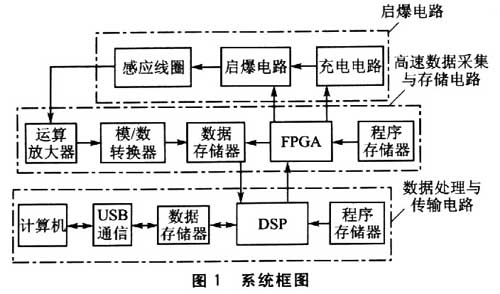

目前國內急需一種能夠對電火工品的發火過程進行實時無損耗監測的方法和手段,并根據監測結果對火工品的可靠性進行準確的判決和認證,解決科研和生產過程中的具體問題。本系統采用感應式線圈作為非接觸式啟爆電流的啟爆裝置,并采用高速A/D、FPGA、DSP等先進的集成電路實現了電火工品的無損耗檢測。其主要目的是:第一,解決電火工品可靠性試驗中微秒級瞬態信號的檢測、處理和存儲技術;第二,為可靠性試驗提供一種在線的無損耗實時檢測系統,以便對電火工品的發火全過程進行監測;第三,為電火工品的發火可靠性認證和評

- 關鍵字:

FPGA DSP A/D

- 1月8日,53歲的Moshe Gavrielov先生接任Xilinx公司63歲的Wim Roelandts,成為公司全球總裁兼首席執行官(CEO)。Roelandts先生將繼續擔任公司董事會主席職務。Gavrielov先生將為Xilinx帶來在半導體和軟件公司高層管理及工程設計方面近30年的經驗,這是由于Gavrielov之前是Cadence公司執行副總裁兼驗證部門總經理,最早在LSI Logic公司工作了近10年。Gavrielov先生上任的第二天,本刊記者通過越洋電話采訪了他。

問:您來自于

- 關鍵字:

IP Xilinx 200802

- ?????? 詳細討論了在MAX plusⅡ開發平臺下使用VHDL硬件描述語言設計現場可編程門陣列(FP-GA)時常見的三個問題:等占空比分頻電路、延時任意量的延時電路、雙向電路。

????? 1 引言

???

?????? 隨著EDA技術的發展,使用硬件語言設計可編程邏輯器件(PLD)/現場可編程門陣

- 關鍵字:

VHDL FPGA 問題

- 概述

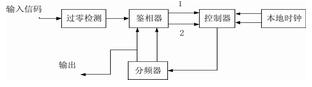

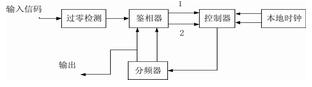

同步是通信系統中一個重要的問題。在數字通信中,除了獲取相干載波的載波同步外,位同步的提取是更為重要的一個環節。因為只有確定了每一個碼元的起始時刻,才能對數字信息作出正確的判決。利用全數字鎖相環可直接從接收到的單極性不歸零碼中提取位同步信號。

一般的位同步電路大多采用標準邏輯器件按傳統數字系統設計方法構成,具有功耗大,可靠性低的缺點。用FPGA設計電路具有很高的靈活性和可靠性,可以提高集成度和設計速度,增強系統的整體性能。本文給出了一種基于fpga的數字鎖相環位同步提取電路。

數

- 關鍵字:

FPGA 鎖相環 分頻器

fpga ip介紹

您好,目前還沒有人創建詞條fpga ip!

歡迎您創建該詞條,闡述對fpga ip的理解,并與今后在此搜索fpga ip的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473