fpga 文章 最新資訊

基于FPGA的簡(jiǎn)易電壓表設(shè)計(jì)

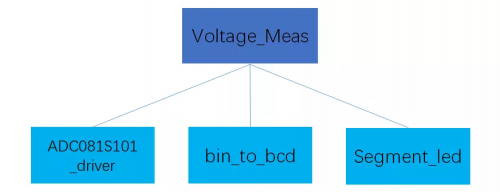

- 傳統(tǒng)的數(shù)字電壓表設(shè)計(jì)通常以大規(guī)模ASIC(專用集成電路)為核心器件,并輔以少量中規(guī)模集成電路及顯示器件構(gòu)成。這種電壓表的設(shè)計(jì)簡(jiǎn)單、精確度高,但是由于采用了ASIC器件使得它欠缺靈活性,其系統(tǒng)功能固定,難以更新擴(kuò)展。而應(yīng)用FPGA設(shè)計(jì)的電壓表,采用FPGA芯片控制通用A/D轉(zhuǎn)換器,可使速度、靈活性大大優(yōu)于通用數(shù)字電壓表。、 本文采用STEP-MAX10M08核心板和STEP Base Board V3.0底板來完成簡(jiǎn)易電壓表設(shè)計(jì),我們將設(shè)計(jì)拆分成三個(gè)功能模塊實(shí)現(xiàn): ADC081S101_driver

- 關(guān)鍵字: FPGA ASIC

基4-FPGA的大動(dòng)態(tài)范圍數(shù)字AGC的實(shí)現(xiàn)

- 1 引言在數(shù)字中頻接收機(jī)中,把A/D轉(zhuǎn)換提前到中頻部分,為保證A/D轉(zhuǎn)換的動(dòng)態(tài)范圍和系統(tǒng)帶寬,要求低噪聲放大器和自動(dòng)增益控制AGC(Automatic Ga

- 關(guān)鍵字: FPGA AGC 動(dòng)態(tài)范圍 數(shù)字

基于FPGA的正交數(shù)字混頻器中數(shù)控振蕩器的設(shè)計(jì)與實(shí)現(xiàn)

- 要CORDIC(COordination Rotation DIgital Computer)算法實(shí)現(xiàn)正交數(shù)字混頻器中的數(shù)控振蕩器的方法。首先推導(dǎo)了算法產(chǎn)生正余弦信號(hào)的實(shí)現(xiàn)過程,然后給出了

- 關(guān)鍵字: FPGA 正交數(shù)字 混頻器 數(shù)控振蕩器

FPGA工作原理與簡(jiǎn)介

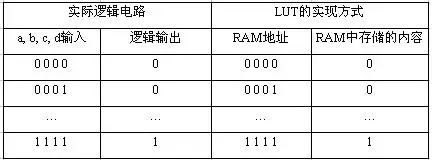

- FPGA工作原理與簡(jiǎn)介 如前所述,F(xiàn)PGA是在PAL、GAL、EPLD、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為ASIC領(lǐng)域中的一種半定制電路而出現(xiàn)的,即解決了定制電路的不足,又克服了原有可編程器件門電路有限的缺點(diǎn)。 由于FPGA需要被反復(fù)燒寫,它實(shí)現(xiàn)組合邏輯的基本結(jié)構(gòu)不可能像ASIC那樣通過固定的與非門來完成,而只能采用一種易于反復(fù)配置的結(jié)構(gòu)。查找表可以很好地滿足這一要求,目前主流FPGA都采用了基于SRAM工藝的查找表結(jié)構(gòu),也有一些軍品和宇航級(jí)FPGA采用Flash或者熔絲與反熔

- 關(guān)鍵字: FPGA Xilinx Altera

常用FPGA/CPLD四種設(shè)計(jì)技巧

- 常用FPGA/CPLD四種設(shè)計(jì)技巧,FPGA/CPLD的設(shè)計(jì)思想與技巧是一個(gè)非常大的話題,本文僅介紹一些常用的設(shè)計(jì)思想與技巧,包括乒乓球操作、串并轉(zhuǎn)換、流水線操作和數(shù)據(jù)接口的同步方法。希望本文能引起工程師們的注意,如果能有意識(shí)地利用這些原則指導(dǎo)日

- 關(guān)鍵字: FPGA CPLD 設(shè)計(jì)技巧

FPGA/EPLD的自上而下設(shè)計(jì)方法

- FPGA/EPLD的自上而下設(shè)計(jì)方法,FPGA/EPLD的自上而下(Top-Down)設(shè)計(jì)方法: 傳統(tǒng)的設(shè)計(jì)手段是采用原理圖輸入的方式進(jìn)行的,如圖1所示。通過調(diào)用FPGA/EPLD廠商所提供的相應(yīng)物理元件庫,在電路原理圖中繪制所設(shè)計(jì)的系統(tǒng),然后通過網(wǎng)表轉(zhuǎn)換產(chǎn)生某一特

- 關(guān)鍵字: FPGA EPLD 自上而下 設(shè)計(jì)方法

不斷演進(jìn)的無源光網(wǎng)絡(luò)(PON)需要FPGA設(shè)計(jì)的靈活性支持

- FPGA技術(shù)、低成本光學(xué)器件以及無源架構(gòu)都為無源光網(wǎng)絡(luò)(PON)以及這些網(wǎng)絡(luò)的演進(jìn)做出了巨大貢獻(xiàn)。系統(tǒng)級(jí)OEM廠商不斷發(fā)現(xiàn),F(xiàn)PGA能夠提供技術(shù)性設(shè)計(jì)和經(jīng)濟(jì)

- 關(guān)鍵字: FPGA PON 無源光網(wǎng)絡(luò)

fpga 介紹

FPGA是英文Field-Programmable Gate Array的縮寫,即現(xiàn)場(chǎng)可編程門陣列,它是在PAL、GAL、EPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個(gè)新概念,內(nèi)部包括可 [ 查看詳細(xì) ]

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司