跳頻通信是擴頻通信的一種主要形式。由于其具有抗干擾、抗截獲的能力,并能做到頻譜資源共享,在當前軍事抗干擾通信系統中被廣泛應用。跳頻通信系統的一項重要參數是頻率的跳變速度。它在很多程度上決定了跳頻通信系統抗跟蹤式干擾的能力,這一點在電子對抗中尤為重要。因此,快速跳頻頻率合成器的設計就成為跳頻通信的關鍵之一。目前頻率合成主有三種方法:直接模擬合成法、鎖相環合成法和直接數字合成法。直接模擬合成法利用倍頻、分頻、混頻及濾波,從單一或幾個參數頻率中產生多個所需的頻率。該方法頻率轉換時間快(小于100ns),但是

關鍵字:

中電科 AD9956 DDS

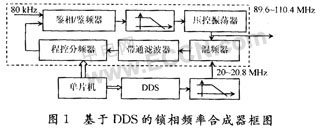

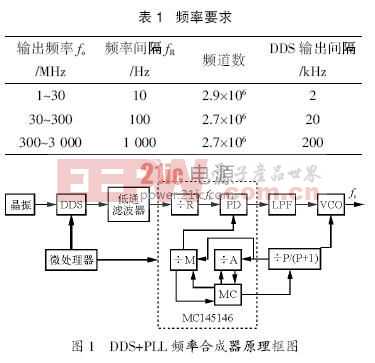

采用DDS內插PLL混頻,即DDS輸出與PLL反饋回路中的壓控振蕩器(VCO)輸出混頻,相當于用DDS取代多環頻率臺成器中的低(細)頻率子環,電路結構簡單,在頻率轉換速度、分辨率等方面性能優良,并且不存在DDS相噪與雜散惡化的問題。本文提出基于該思想的一種VHF段頻率合成器設計。

關鍵字:

DDS,鎖相頻率合成器

采用DDS內插PLL混頻,即DDS輸出與PLL反饋回路中的壓控振蕩器(VCO)輸出混頻,相當于用DDS取代多環頻率臺成器中的低(細)頻率子環,電路結構簡單,在頻率轉換速度、分辨率等方面性能優良,并且不存在DDS相噪與雜散惡化的問題。本文提出基于該思想的一種VHF段頻率合成器設計。

關鍵字:

DDS,鎖相頻率合成器

1 引 言

現代頻半合成源對頻率精度、分辨率、轉換時間和頻譜純度等指標提出了越來越高的要求。甚高頻(VHF)頻率合成器通常采用多鎖相環路(PLL)結構,多環合成器將單環中的巨大分頻比用多個環路來負擔,同時各環,尤其足主環的鑒相頻率大幅度提高,從而滿足了鑒相頻率高、分頻比小和分辨率高等要求。但是由于多環組合的固有特性,尤其是分辨率每提高1個數量級,就要增加一級子環路,使得其頻率轉換速度低、線路復雜、可靠性差。

直接數字式頻率合成技術(DDS)的頻率分辨率高、頻率轉換速度快。DDS/PLL混合

關鍵字:

DDS 鎖相頻率 合成器 模擬IC

1.引言

測量時,由于種種原因,被測物理量的測量結果總是偏離真值。這種偏差就叫做誤差。

測量誤差可分為隨機誤差、系統誤差、粗大誤差三類。

在同一測量條件下,多次重復測量同一量值時,每次測量誤差的絕對值和符號都以不可預知的方式變化的誤差,稱為隨機誤差。隨機誤差由對測量值影響微小但卻互不相關的大量因素共同造成。

在同一測量條件下,多次測量重復同一量時,測量誤差的絕對值和符號都保持不變,或在測量條件改變時按一定規律變化的誤差,稱為系統誤差。

粗大誤差是一種顯然與實際值不符的誤差

關鍵字:

測試 測量 TS9980 S1 測試測量

1 引 言

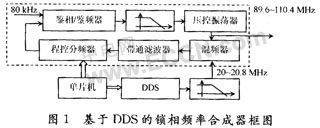

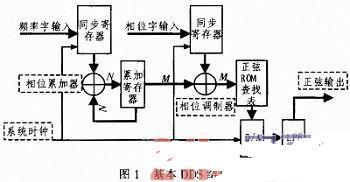

直接數字頻率合成技術(Direel Digital FrequencySynthesis,DDS)稱為第三代頻率合成技術,他利用正弦信號的相位與時間呈線性關系的特性,通過查表的方式得到信號的瞬時幅值,從而實現頻率合成。這種方法不僅可以產生不同頻率的正弦波,而且具有超寬的相對帶寬,超高的變頻速率,超細的分辨率以及相位的連續性和產生任意波形(AWG)的特點。

目前所使用的大部分DDS結構,在相位累加模塊和相位幅度轉換模塊均采用了流水線技術和某些壓縮算法等,但都不能從根本上解決DDS

關鍵字:

嵌入式系統 單片機 數字頻率合成 DDS MCU和嵌入式微處理器

1 引 言

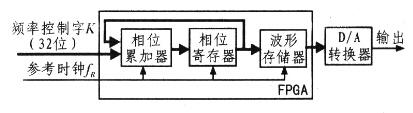

DDS(Direct Digital Frequency Synthesis,直接數字頻率合成器)是一種從相位概念出發直接合成所需波形的頻率合成技術。由于DDS具有相對頻帶寬、頻率分辨率高、頻率變化速度快與相位可連續線性變化等一系列特點,已被廣泛應用于數字通信系統中。目前,可供用戶選擇的高性能、多功能的專用DDS芯片比較多。然而在某些對控制方式、置頻速率等方面有特殊要求的場合,設計一個基于高性能FPGA(Field Programming Gate Array,現場可編程門陣列)的D

關鍵字:

嵌入式系統 單片機 DDS 混合仿真 MCU和嵌入式微處理器

摘要:在分析了DDS基本原理以及AD9858基本特點的基礎上,介紹了AD9858的送數方式及單片機接口程序。給出了利用AD9858內部寄存器來實現跳頻時間小于50ns的4頻點快速跳頻的具體方法。

關鍵詞:DDS;AD9858;快速跳頻

在電子系統中,常常需要應用頻率合成技術來實現跳頻源設計。頻率合成指對一個高穩定的參考頻率進行各種技術處理,以生成一系列穩定的頻率輸出。目前應用最廣的是鎖相環(PLL)頻率合成技術,它是通過改變PLL中的分頻比N來實現跳頻的

關鍵字:

DDS AD9858 快速跳頻 MCU和嵌入式微處理器

引言

在現代科研機構電路設計、大專院校的電子系統教學中,集成運算放大器作為信號處理的基本器件,應用非常廣泛,準確的掌握集成運放的參數是進行電子系統設計的基本前提。為了方便用戶準確掌握手中運放的各項參數,本文提供了一種采用可編程DDS芯片和MCU的測量系統,可自動測量集成運放的5項基本參數,以小液晶屏顯示測量結果,并可根據需要打印測量的結果,與現有的BJ3195等昂貴測試儀相比,該測量系統功能精簡、操作智能化、人機接口友好。

關鍵字:

嵌入式系統 單片機 DDS MCU 運算放大器 嵌入式

直接數字合成器,是采用數字技術的一種新型頻率合成技術,他通過控制頻率、相位增量的步長,產生各種不同頻率的信號。他具有一系列的優點;較高的頻率分辨率;可以實現快速的頻率切換;在頻率改變時能夠保持相位的連續;很容易實現頻率、相位和幅度的數控調制等。目前可采用專用芯片或可編程邏輯芯片實現DDS[1],專用的DDS芯片產生的信號波形、功能和控制方式固定,常不能滿足具體需要[2]。可編程邏輯器件具有器件規模大、工作速度快及可編程的硬件特點,并且開發周期短,易于升級,因為非常適合用于實現DDS。

1 DDS的

關鍵字:

嵌入式系統 單片機 DSP Builder DDS FPGA 嵌入式

摘要: 給出一種利用AD9959多通道DDS同步特性,簡化測控通信系統中多路DDS同步設計的方案,與原有方案相比具有控制方式靈活、外圍元件少,性能優良等優點。關鍵詞: DDS;同步;AD9959;測控通信

引言近年來,為了提高信息傳輸速率,增強通信抗干擾能力,飛行器測控通信系統已從統一載波體制向擴頻統一測控通信體制發展。但是,這種寬帶擴頻測控技術的應用使得同步設計成為系統實現的難點,尤其對于多頻率源系統,信號之間的嚴格同步更為困難。一般情況下,為了獲得多路DDS的同步,設計者往往會使

關鍵字:

0704_A AD9959 DDS 測控通信 工業控制 同步 雜志_設計天地 工業控制

介紹了一種基于計算機ISA總線、三路同步的DDS信號源的設計。對信號源與ISA總線的接口關系以及多路DDS的同步問題進行了討論。測試結果表明,該信號源的各路DDS具有較好的同步關系和相位噪聲指標。

關鍵字:

ISA DDS 總線 多路

本文研究并實現了基于FPGA(FieldProgrammableGateArray)的智能動態信號源,采用了DDS(DirectDigitalSynt...

關鍵字:

DDS 頻譜 諧波 正弦

王仁發,林秩盛,陸南昌,熊 燕(中山大學 電子與通信工程系, 廣州 510275) 摘 要:研究了DDS+雙PLL構成的新型數字調諧系統:A環產生DDS所需的時鐘信號,B環產生高頻輸出。B環使調諧器輸出頻率f0作較大變化,A環和DDS使f0作小變動。該系統工作頻率為850MHz~925MHz和1700MHz~1850MHz,頻率分辨率可達25kHz。在單片微機控制下,可實現跳頻。 關鍵詞:數字調諧系統 DDS PLL 跳頻

數字調諧系統是現代收發信機的核心,其性能直接影響通信質

關鍵字:

DDS PLL 數字調諧系統 跳頻

dds-s1介紹

您好,目前還沒有人創建詞條dds-s1!

歡迎您創建該詞條,闡述對dds-s1的理解,并與今后在此搜索dds-s1的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473