ddr 文章 最新資訊

DDR內(nèi)存的發(fā)展簡史:和三星有關(guān)

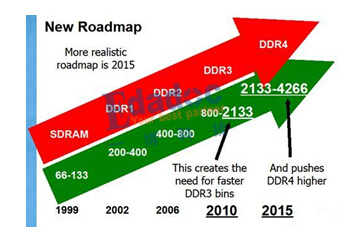

- DDR的種類: 1、DDR SDRAM:Double Data Rate Synchronous Dynamic Random Access Memory,雙倍數(shù)據(jù)率同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器; 2、DDR2 SDRAM:Double-Data-Rate Two Synchronous Dynamic Random Access Memory,第二代雙倍數(shù)據(jù)率同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器; 3、DDR3 SDRAM:Double-Data-Rate Three Synchronous Dynamic Ra

- 關(guān)鍵字: DDR 三星

控制DDR線長匹配來保證時(shí)序,在PCB設(shè)計(jì)時(shí)應(yīng)該這么做!

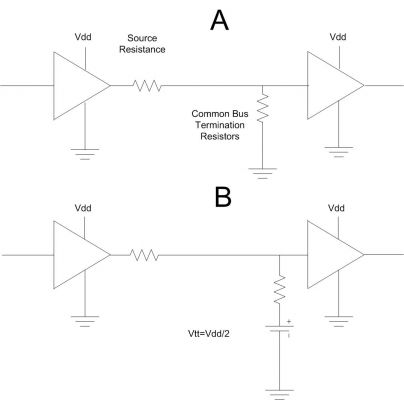

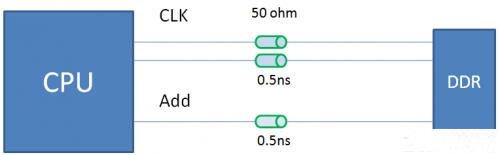

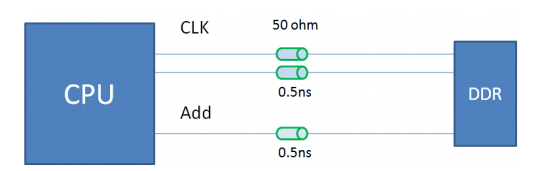

- DDR布線在PCB設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的時(shí)序裕量。要保證系統(tǒng)的時(shí)序,線長匹配又是一個(gè)重要的環(huán)節(jié)。我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制/命令信號(hào)與時(shí)鐘做等長。數(shù)據(jù)信號(hào)與DQS做等長。為啥要做等長?大家會(huì)說是要讓同組信號(hào)同時(shí)到達(dá)接收端,好讓接收芯片能夠同時(shí)處理這些信號(hào)。那么,時(shí)鐘信號(hào)和地址同時(shí)到達(dá)接收端,波形的對(duì)應(yīng)關(guān)系是什么樣的呢?我們通過仿真來看一下具體波形。 建立如下通道,分別模擬DDR3的地址信號(hào)與時(shí)鐘信號(hào)。

- 關(guān)鍵字: PCB DDR

DDR布線舉足輕重,一文看懂背后的大學(xué)問

- DDR布線在PCB設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的時(shí)序裕量。要保證系統(tǒng)的時(shí)序,線長匹配又是一個(gè)重要的環(huán)節(jié)。我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制/命令信號(hào)與時(shí)鐘做等長。數(shù)據(jù)信號(hào)與DQS做等長。為啥要做等長?大家會(huì)說是要讓同組信號(hào)同時(shí)到達(dá)接收端,好讓接收芯片能夠同時(shí)處理這些信號(hào)。那么,時(shí)鐘信號(hào)和地址同時(shí)到達(dá)接收端,波形的對(duì)應(yīng)關(guān)系是什么樣的呢?我們通過仿真來看一下具體波形。 建立如下通道,分別模擬DDR3的地址信號(hào)與時(shí)鐘信號(hào)。

- 關(guān)鍵字: DDR 布線

基于MIMO技術(shù)的視頻緩存器設(shè)計(jì)方案

- 隨著高速處理器的不斷發(fā)展,嵌入式系統(tǒng)應(yīng)用的領(lǐng)域越來越廣泛,高速大容量緩存器被廣泛應(yīng)用于音視頻系統(tǒng)中,然而專用的高速大容量緩存芯片價(jià)格過于昂貴,傳統(tǒng)SDRAM在帶寬上已經(jīng)逐漸無法滿足應(yīng)用.

- 關(guān)鍵字: MIMO技術(shù) 視頻緩存器 DDR

基于FPGA的LCoS顯示驅(qū)動(dòng)系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

- 研究了硅基液晶(LCoS)場序彩色顯示驅(qū)動(dòng)系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn).該系統(tǒng)以FPGA作為主控芯片,用兩片高速DDR2 SDRAM作為幀圖像存儲(chǔ)器.通過對(duì)圖像數(shù)據(jù)以幀為單位進(jìn)行處理,系統(tǒng)將并行輸入的紅、綠、藍(lán)數(shù)據(jù)轉(zhuǎn)換成申行輸出的紅、綠、藍(lán)單色子幀.將該驅(qū)動(dòng)系統(tǒng)與投影光機(jī)配合,實(shí)現(xiàn)了分辨率為800×600的LCoS場序彩色顯示.

- 關(guān)鍵字: 硅基液晶 DDR FPGA

利用新一代虛擬探測(cè)功能實(shí)現(xiàn)DDR等信號(hào)去嵌測(cè)試

- 一、內(nèi)存測(cè)試中的難點(diǎn)內(nèi)存廣泛應(yīng)用于各類電子產(chǎn)品中,內(nèi)存測(cè)試也是產(chǎn)品測(cè)試中的熱點(diǎn)和難點(diǎn)。內(nèi)存測(cè)試中最為關(guān)鍵的測(cè)試項(xiàng)目為DQ/DQS/CLK之間的時(shí)序關(guān)系。JEDEC規(guī)范規(guī)定測(cè)量這幾個(gè)信號(hào)之間的時(shí)序時(shí)測(cè)試點(diǎn)需要選擇在靠

- 關(guān)鍵字: 虛擬探測(cè) DDR 信號(hào)去嵌測(cè)試

高速存儲(chǔ)器的調(diào)試和評(píng)估――不要僅僅停留在一致性測(cè)試上

- 引言:DDR4 等存儲(chǔ)技術(shù)的發(fā)展帶動(dòng)存儲(chǔ)器速度與功率效率空前提升,僅僅停留在一致性測(cè)試階段,已經(jīng)不能滿足日益深入的調(diào)試和評(píng)估需求。DDR 存儲(chǔ)器的測(cè)試項(xiàng)目涵蓋了電氣特性和時(shí)序關(guān)系,由JEDEC明確定義,JEDEC 規(guī)范并

- 關(guān)鍵字: 高速存儲(chǔ)器 一致性測(cè)試 DDR

DDR的前世與今生(二)

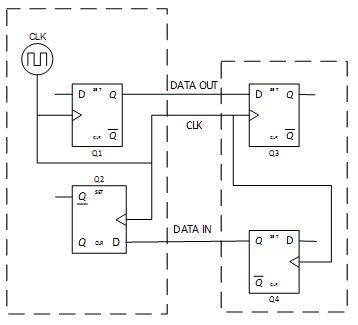

- SDRAM與DDR SDRAM SDRAM是比較久遠(yuǎn)的事情了,但我們一說到它肯定不會(huì)和 DDR混淆,我們通常理解的SDRAM其實(shí)是SDR SDRAM,為SDRAM的第一代,而DDR1則為第二代,乃至到我們現(xiàn)在使用的DDR4,其實(shí)為第五代SDRAM,在此需要澄清一下。以示區(qū)別,后續(xù)文 章里面用SDR來特指SDR SDRAM,而DDR就特指DDR SDRAM了。 就像很多人回復(fù)的一樣,他們的本質(zhì)區(qū)別就是周期操作方 式(也稱時(shí)鐘采樣)的差異,這就導(dǎo)致后面設(shè)計(jì)上很大的不同。SDR都是“

- 關(guān)鍵字: DDR SDRAM

ddr介紹

DDR=Double Data Rate雙倍速內(nèi)存

嚴(yán)格的說DDR應(yīng)該叫DDR SDRAM,人們習(xí)慣稱為DDR,部分初學(xué)者也常看到DDR SDRAM,就認(rèn)為是SDRAM。DDR SDRAM是Double Data Rate SDRAM的縮寫,是雙倍速率同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器的意思。DDR內(nèi)存是在SDRAM內(nèi)存基礎(chǔ)上發(fā)展而來的,仍然沿用SDRAM生產(chǎn)體系,因此對(duì)于內(nèi)存廠商而言,只需對(duì)制造普通SD [ 查看詳細(xì) ]

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司