現場可編程門陣列(FPGA)器件廣泛用于數字信號處理領域.而使用VHDL或VerilogHDL語言進行設計的難度較大。提出一種采用DSP Builder實現FIR濾波器的設計方案,按照Matlab/Simulink/DSP Builder/Modelsim/QuartusⅡ的設計流程,設計一個16階的FIR低通濾波器,并完成了軟硬件的仿真與驗證。結果表明,該方法簡單易行,可滿足設計要求,它驗證了采用DSP Builder實現濾波器設計的獨特優勢。

關鍵字:

Builder DSP FIR 濾波器

基于DSP Builder的腦電信號小波處理,1 引言

關鍵字:

小波 處理 電信號 Builder DSP 基于 DSP

設計分析了Chirp函數在時域和頻域內的一般特點和解析公式。提出首先在Altera DSP開發工具DSP Builder中實現直接數字合成器(DDS)模塊,根據Chirp函數特定的輸入/輸出(線性和非線性)關系,計算出當前輸入字與輸出頻率的對應關系;然后設計控制字子模塊產生DDS模塊的頻率控制字,驅動DDS產生不同的輸出頻率,通過在Matlab的Simu-link環境下的仿真驗證,得出不同時刻輸出的頻譜圖,驗證了該設計能很好地實現Chirp信號源。

關鍵字:

Builder Chirp DSP 信號源

實現信號源常用的方法是頻率合成法,其中直接數字頻率合成法是繼直接頻率合成法和間接頻率合成法之后,隨著電子技術迅速發展的第三代頻率合成技術。DDS是一種全數字技術,它從相位概念出發直接合成所需頻率,它具有頻

關鍵字:

Builder FPGA DSP 正弦

1 引言 傳統的波形發生器多采用模擬分立元件實現,產生的波形種類要受到電路硬件的限制,體積大,靈活性和穩定性也相對較差。采用FPGA器件直接實現多種波形信號發生器,配以相應的外圍器件實現的波形發生器具

關鍵字:

Builder Matlab DSP 多波形

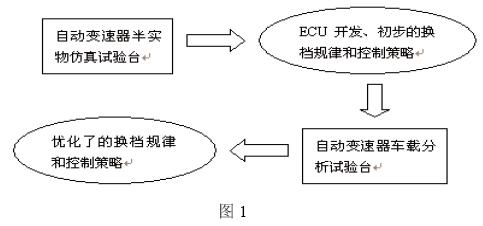

摘要 本文闡述了基于Borland C++ Builder開發的自動變速器電控單元(ECU)實車試驗的數據采集系統,通過對系統硬件結構、軟件編制核心步驟的描述,詳細介紹了系統的開發過程。本數據采集系統為自動變速器電控單元的開發提供了重要的測試平臺。

關鍵詞 C++ Builder,電控單元,數據采集,液力自動變速器

1 引言

液力自動變速器是將車速和節氣門開度等車輛的狀態信號作為電控單元(ECU)的輸入信號,經電控單元識別判斷處理后,根據換檔規律,發出信號給相應電磁閥,利用電磁閥控制油壓回路

關鍵字:

ECU C++ Builder 電控單元 數據采集 液力自動變速器

面向高性能數字信號處理(DSP)設計,Altera公司發布具有第二代模型綜合技術的DSP Builder工具8.0。該技術使DSP設計人員第一次能夠自動生成基于高級Simulink設計描述的時序優化RTL代碼。借助這一新的DSP Builder,設計人員在幾分鐘內就可以實現接近峰值FPGA性能的高性能設計。和手動優化HDL代碼需要數小時甚至數天時間相比,這大大提高了效能。

The MathWorks信號處理和通信市場總監Ken Karnofsky評論說:“DSP Builder是第二

關鍵字:

Altera DSP Builder RF 嵌入式

數字濾波器在數字信號處理的各種應用中發揮著十分重要的作用,他是通過對采樣數據信號進行數學運算處理來達到頻域濾波的目的。數字濾波器既可以是有限長單脈沖響應(FIR)濾波器也可以是無限長單脈沖響應(IIR)濾波器。在維納濾波器理論發明的早期,人們使用IIR濾波器,但現在更多是使用FIR濾波器。本文按照Matlab/Simulink/DSP Builder/QuartusⅡ流程,設計一個FIR濾波器。Altera DSP Builder是連接Simulink和QuartusⅡ開發軟件的DSP開發工具。在DSP

關鍵字:

濾波器 設計 FIR Builder DSP 基于

為幫助系統級設計人員在FPGA軟核處理器上有更多的選擇,Altera公司(NASDAQ: ALTR)今天宣布,Freescale將為SOPC Builder工具推出32位V1 ColdFire軟核。為迅速方便的使用Altera® Cyclone® III FPGA建立系統級設計,設計人員現在使用SOPC Builder工具時,可以選擇Freescale®、ARM®或者Altera軟核處理器以及50多種其他的知識產權(IP)模塊。

SOPC Builder是獨特的A

關鍵字:

Altera SOPC Builder 軟核 Freescale FPGA

引言 隨著電子技術的發展,VGA(視頻圖形陣列)接口出現在很多嵌入式平臺上,用于圖像信息的實時顯示等。在某些情況下,設計者希望通過普通的顯示器或投影儀觀測FPGA內部的一些矢量信號,即把帶VGA接口的顯示器當作示波器使用等,這就需要對數據進行處理,使之能夠在顯示器上實時顯示。 本文基于DSP Builder的VGA接口設計方法,對VGA接口時序和系統設計需求進行了介紹,并在硬件平臺下實現一維與二維信號的顯示。 VGA接口標準 VGA顯像原理 顯示器通過光柵掃描的方

關鍵字:

DSP Builder VGA 接口 嵌入式系統 嵌入式

摘 要:本文給出了基于Altera DSP Builder平臺下VGA接口的系統級設計方法。該接口模塊可利用NiosⅡ進行靈活地控制和配置。文中在CycloneⅡ DSP平臺上實現了該設計并驗證了設計的有效性。

關鍵詞:VGA;DSP Builder;SOPC;行頻;場頻

引言

隨著電子技術的發展,VGA(視頻圖形陣列)接口出現在很多嵌入式平臺上,用于圖像信息的實時顯示等。在某些情況下,設計者希望通過普通的顯示器或投影儀觀測FPGA內部的一些矢量信號,即把帶VGA接口的顯示器當作示波

關鍵字:

嵌入式系統 單片機 :VGA DSP Builder 行頻 MCU和嵌入式微處理器

摘 要:本文從系統總線設計、用戶自定義指令和FPGA協處理器的應用這三個方面詳細介紹了如何應用SoPC設計思想和SoPC Builder工具來開發電子系統。通過應用SoPC Builder開發工具,設計者可以擺脫傳統的、易于出錯的軟硬件設計細節,從而達到加快項目開發、縮短開發周期、節約開發成本的目的。

關鍵詞:SoPC;SoPC Builder;FPGA 引言 隨著技術的進一步發展,SoC設計面臨著一些諸如如何進行軟硬件協同設計,如何縮短電子產品開發周

關鍵字:

SoPC Builder FPGA 軟硬件設計 系統總線 其他IC 制程

builder介紹

您好,目前還沒有人創建詞條builder!

歡迎您創建該詞條,闡述對builder的理解,并與今后在此搜索builder的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473