EEPW首頁(yè) >>

主題列表 >>

asic-to-fpga

asic-to-fpga 文章 最新資訊

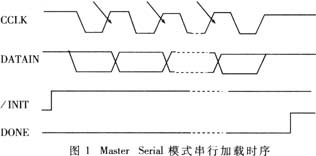

采用EEPROM對(duì)大容量FPGA芯片數(shù)據(jù)實(shí)現(xiàn)串行加載

- 自大規(guī)模現(xiàn)場(chǎng)可編程邏輯器件問(wèn)世以來(lái),先后出現(xiàn)了兩類器件,一類是基于SRAM體系結(jié)構(gòu)的FPGA系列,如XILINX公司的4000系列和最新的Virtex系列;另一類是基于faxtFLASH技術(shù)的CPLD器件,如XILINX公司的9500系列和Lattice公司的ispLSxx系列芯片。FPGA具有容量大、設(shè)計(jì)資源豐富、片內(nèi)ROM及RAM設(shè)計(jì)靈活等特點(diǎn)1,但是它們需要在每次上電時(shí)進(jìn)行數(shù)據(jù)加載。目前實(shí)現(xiàn)加載的方法有以下三種:①采用PROM并行加載;②采用專用SROM串行加載;③采用單片機(jī)控制實(shí)現(xiàn)加載。

- 關(guān)鍵字: FPGA XILINX CPLD 數(shù)據(jù)加載 EEPROM

基于USB的ARINC429總線接口模塊設(shè)計(jì)

- 引言 ARINC429總線由美國(guó)航天無(wú)線電設(shè)備公司所資助,是廣泛應(yīng)用于當(dāng)前航空電子設(shè)備中的一種數(shù)據(jù)總線傳輸標(biāo)準(zhǔn)。與傳統(tǒng)的航空電子設(shè)備間的模擬傳輸相比,ARINC429總線具有抗干擾能力強(qiáng)、傳輸精度高、傳輸線路少以及成本低等優(yōu)點(diǎn)。ARINC數(shù)據(jù)總線協(xié)議規(guī)定一個(gè)數(shù)據(jù)由32位組成,采用雙極性歸零碼,以12.5Kb/s或100Kb/s碼速率傳輸。本設(shè)計(jì)利用USB即插即用、FPGA可靈活配置等特點(diǎn),設(shè)計(jì)了基于USB總線的ARINC429總線接口模塊。 接口模塊總體設(shè)計(jì)結(jié)構(gòu) 接口

- 關(guān)鍵字: 接口 FPGA USB 總線

基于AD9957的USB側(cè)音測(cè)距信號(hào)發(fā)生器設(shè)計(jì)

- 0 引言 隨著我國(guó)航天技術(shù)的不斷進(jìn)步,深空測(cè)距技術(shù)受到越來(lái)越多的關(guān)注。在深空測(cè)距系統(tǒng)中,中頻信號(hào)發(fā)生器對(duì)系統(tǒng)性能有著重要的意義。在USB(統(tǒng)一S頻段)系統(tǒng)中,原有的模擬電路實(shí)現(xiàn)的發(fā)射模塊存在性能不完善、輸入動(dòng)態(tài)范圍小、可控性能差、不能適應(yīng)中心頻率大范圍變化、體積大等問(wèn)題,為了解決上述問(wèn)題,可在一個(gè)標(biāo)準(zhǔn)化通用數(shù)字調(diào)制信號(hào)發(fā)生器的平臺(tái)上,通過(guò)外圍的控制電路,實(shí)現(xiàn)對(duì)載波中心頻率、輸出功率、調(diào)相指數(shù)、測(cè)距音通/斷控制等參數(shù)的改變。 以軟件無(wú)線電思想為核心,基于PLD(可編程邏輯器件)的通用調(diào)制信號(hào)

- 關(guān)鍵字: 測(cè)距 PLD USB D/A FPGA

基于FPGA的自然對(duì)數(shù)變換器的設(shè)計(jì)與實(shí)現(xiàn)

- 本文利用CORD IC算法在FPGA上實(shí)現(xiàn)了自然對(duì)數(shù)運(yùn)算器。實(shí)驗(yàn)結(jié)果表明該對(duì)數(shù)運(yùn)算器的輸出誤差為10-4數(shù)量級(jí),最高頻率可達(dá)到80MHz。該運(yùn)算器適用于高速大數(shù)據(jù)量的數(shù)據(jù)處理。

- 關(guān)鍵字: FPGA 對(duì)數(shù)運(yùn)算 CORD IC算法 對(duì)數(shù)變換器 200808

Altera FPGA開發(fā)板為XLoom提供誤碼率測(cè)試環(huán)境

- 進(jìn)一步展示其FPGA靈活性和通用性,Altera公司宣布,XLoom通信公司采用Stratix® II GX FPGA信號(hào)完整性開發(fā)套件來(lái)提供獨(dú)特的誤碼率(BER)測(cè)試環(huán)境。和傳統(tǒng)的BER測(cè)試設(shè)備相比,Altera基于FPGA的開發(fā)板支持XLoom以更高的性價(jià)比來(lái)測(cè)試芯片級(jí)光電互聯(lián)模塊。這一獨(dú)特的測(cè)試環(huán)境更貼近實(shí)際的客戶狀態(tài),同時(shí)進(jìn)一步節(jié)省了空間,降低了功耗。 傳統(tǒng)的BER測(cè)試儀成本高達(dá)100,000美元,而Stratix II GX FPGA信號(hào)完整性開發(fā)套件在這方面的成本節(jié)省了90%

- 關(guān)鍵字: Altera FPGA 開發(fā)套件 XLoom

基于FPGA的空間存儲(chǔ)器的糾錯(cuò)系統(tǒng)

- 1、引言 阿爾法磁譜儀(Alpha Magnetic Spectrometer,AMS)實(shí)驗(yàn)室是丁肇中博士領(lǐng)導(dǎo)的由美、俄、德、法、中等16個(gè)國(guó)家和地區(qū)共300多名科學(xué)家參加的大型國(guó)際合作項(xiàng)目。它是國(guó)際空間站上唯一大型物理實(shí)驗(yàn),是人類第一次在太空中精密地測(cè)量高能量帶電原子核粒子的實(shí)驗(yàn)。其目的是為尋找反物質(zhì)所組成的宇宙和暗物質(zhì)的來(lái)源以及測(cè)量宇宙線的來(lái)源。 但是對(duì)于AMS實(shí)驗(yàn)的空間電子系統(tǒng),同樣會(huì)受到高能粒子的襲擊,導(dǎo)致存儲(chǔ)器的內(nèi)容發(fā)生變化,改寫半導(dǎo)體存儲(chǔ)器件的邏輯狀態(tài),導(dǎo)致存儲(chǔ)單元在邏輯&ls

- 關(guān)鍵字: FPGA 存儲(chǔ)器 AMS 編碼 譯碼

Actel推出Libero集成開發(fā)環(huán)境 8.4

- Actel公司宣布其Libero® 集成開發(fā)環(huán)境 (IDE) 增添全新的功耗優(yōu)化和增強(qiáng)的設(shè)計(jì)創(chuàng)建功能。全新的Libero IDE 8.4針對(duì)基于 Flash的IGLOO®、IGLOO PLUS和 ProASIC®3L現(xiàn)場(chǎng)可編程門陣列 (FPGA),提供由1.14V至 1.575V的FPGA內(nèi)核工作電壓范圍,為設(shè)計(jì)人員提供額外的內(nèi)核電壓選擇,以實(shí)現(xiàn)更低的功耗。新版本Libero IDE改進(jìn)了SmartPower功耗分析工具,便于比較同一設(shè)計(jì)的多種設(shè)計(jì)實(shí)現(xiàn)和器件不同工作條件下的狀況

- 關(guān)鍵字: Actel IDE Libero FPGA 集成開發(fā)環(huán)境

Altera在40nm:抖動(dòng)、信號(hào)完整性、功耗和工藝達(dá)到最佳的收發(fā)器

- 1. 引言 在摩爾定律的推動(dòng)下,半導(dǎo)體行業(yè)技術(shù)發(fā)展非常迅速,集成電路晶體管數(shù)量每?jī)赡攴叮瑢?duì)器件或者系統(tǒng)之間的通信鏈路數(shù)據(jù)速率要求越來(lái)越高。而工藝節(jié)點(diǎn)的減小又促進(jìn)了摩爾定律。減小體積可以在單位邏輯中容納更多的功能,提高工作速率、邏輯密度和集成度,同時(shí)降低了。通常采用高級(jí)設(shè)計(jì)方法和工藝技術(shù)來(lái)提高數(shù)據(jù)速率,支持固網(wǎng)和無(wú)線通信、計(jì)算機(jī)、存儲(chǔ)、軍事應(yīng)用以及廣播電子系統(tǒng)發(fā)送接收大量數(shù)據(jù),以滿足不斷增長(zhǎng)的數(shù)據(jù)傳輸和帶寬要求。 微處理器和FPGA等前沿產(chǎn)品采用了65-nm工藝技術(shù)。這些產(chǎn)品的后續(xù)型號(hào)將采

- 關(guān)鍵字: 半導(dǎo)體 FPGA 微處理器 I/O

ARM7與FPGA在工業(yè)控制的結(jié)合

- 工業(yè)控制中往往需要完成多通道故障檢測(cè)及多通道命令控制(這種多任務(wù)設(shè)置非常普遍),單獨(dú)的CPU芯片由于其外部控制接口數(shù)量有限而難以直接完成多路檢控任務(wù),故利用ARM芯片與FPGA相結(jié)合來(lái)擴(kuò)展檢控通道是一個(gè)非常好的選擇。這里介紹用Atmel公司ARM7處理器(AT91FR40162)和ALTERA公司的低成本FPGA芯片(cyclone2)結(jié)合使用完成多通道檢控任務(wù)的一種實(shí)現(xiàn)方法。 各部分功能簡(jiǎn)介 圖1為此系統(tǒng)的結(jié)構(gòu)連接框圖。如圖所示,ARM芯片與FPGA芯片之間通過(guò)數(shù)據(jù)總線、地址總線及讀寫控

- 關(guān)鍵字: 工業(yè)控制 ARM FPGA 處理器

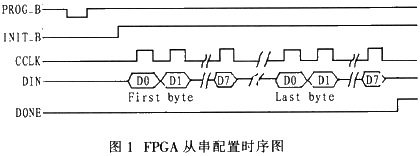

基于ARM的嵌入式系統(tǒng)中從串配置FPGA的實(shí)現(xiàn)

- 1 引言 ARM(Advanced RISC Machines)既可以認(rèn)為是一個(gè)公司。也可以認(rèn)為是對(duì)一類微處理器的統(tǒng)稱,還可以認(rèn)為是一項(xiàng)技術(shù)。基于ARM技術(shù)的微處理器應(yīng)用約占據(jù)了32位RISC微處理器75%以上的市場(chǎng)份額,ARM技術(shù)正在逐步滲入到人們生活的各個(gè)方面[1]。到目前為止,ARM微處理器及技術(shù)已經(jīng)廣泛應(yīng)用到各個(gè)領(lǐng)域,包括工業(yè)控制領(lǐng)域、網(wǎng)絡(luò)應(yīng)用、消費(fèi)類電子產(chǎn)品、成像和安全產(chǎn)品等。 FPGA(Field Programmable Gate Array)是一種高密度現(xiàn)場(chǎng)可編程邏輯器件,

- 關(guān)鍵字: ARM 嵌入式 FPGA SRAM

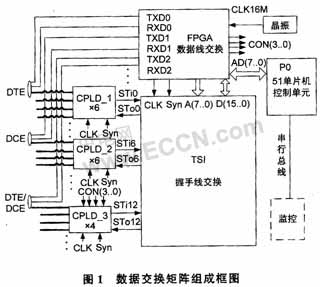

基于FPGA的數(shù)據(jù)無(wú)阻塞交換設(shè)計(jì)

- 0 引言 隨著FPGA和大規(guī)模集成電路的發(fā)展,數(shù)據(jù)交換的實(shí)現(xiàn)有了新的方法。在該設(shè)計(jì)中,F(xiàn)PGA完成串口數(shù)據(jù)信號(hào)(TXD、RXD)的交換,專用的時(shí)隙交換芯片完成串口握手線(RTS、CTS、DTR、DSR、DCD、RI)的交換。內(nèi)部有硬件沖突監(jiān)測(cè)功能,能夠自動(dòng)檢測(cè)到2個(gè)終端同時(shí)連接到同一個(gè)信道或2個(gè)信道連接到同一個(gè)終端,并自動(dòng)將舊的連接狀態(tài)拆除,建立新的鏈路。這樣就使原來(lái)的連接終端進(jìn)入空閑狀態(tài),保證終端和信道時(shí)間軸上的無(wú)縫隙切換。通過(guò)判斷RI的狀態(tài),它還可以監(jiān)視信道DCE的狀態(tài),判斷出信道是否有請(qǐng)求

- 關(guān)鍵字: FPGA 集成電路 數(shù)據(jù)交換 串口

FPGA躋身汽車系統(tǒng)關(guān)鍵應(yīng)用領(lǐng)域

- 消費(fèi)者迫切需求的輔助駕駛系統(tǒng)技術(shù)需要具有先進(jìn)精密功能且外形尺寸又非常小的高可靠性元件。由于這些系統(tǒng)尺寸很小,而且彼此非常靠近,因此還要求器件具有超低功耗和良好的耐久性。空間受限的系統(tǒng)在設(shè)計(jì)方面存在的熱可靠性問(wèn)題可通過(guò)采用較少的元件及超低的功耗來(lái)解決。Actel公司以Flash為基礎(chǔ)的ProASIC3 FPGA具有固件錯(cuò)誤免疫力、低功耗和小外形尺寸等優(yōu)勢(shì),因而消除了FPGA(現(xiàn)場(chǎng)可編程門陣列)用于安全關(guān)鍵汽車應(yīng)用領(lǐng)域的障礙。 汽車工程師過(guò)去通常依賴于MCU(微控制器)和定制ASIC(專用集成電

- 關(guān)鍵字: FPGA ASIC MCU ProASIC3 半導(dǎo)體器件

基于FPGA+DSP的實(shí)時(shí)圖像處理平臺(tái)的設(shè)計(jì)與實(shí)現(xiàn)

- 藥用管制瓶在灌裝前必須進(jìn)行多個(gè)指標(biāo)檢測(cè)。針對(duì)實(shí)際生產(chǎn)的需要,基于FPGA和DSP,提出并設(shè)計(jì)了小型化、低功耗的多通道高速實(shí)時(shí)圖像采集、處理和顯示系統(tǒng)。給出了影響系統(tǒng)性能的主要因素。

- 關(guān)鍵字: 平臺(tái) 設(shè)計(jì) 實(shí)現(xiàn) 圖像處理 實(shí)時(shí) FPGA DSP 基于

asic-to-fpga介紹

您好,目前還沒有人創(chuàng)建詞條asic-to-fpga!

歡迎您創(chuàng)建該詞條,闡述對(duì)asic-to-fpga的理解,并與今后在此搜索asic-to-fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)asic-to-fpga的理解,并與今后在此搜索asic-to-fpga的朋友們分享。 創(chuàng)建詞條

熱門主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司