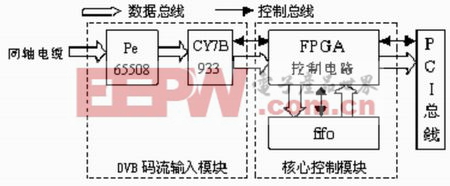

- 基于PCI IP核的碼流接收卡的設計,本文介紹了一種基于Altera公司的PCI接口IP核的DVB碼流接收系統的硬件設計方案及設計要點的分析。該設計采用Altera公司的新一代FPGA芯片EP1C12和PCI IP核以及高速串行數據通信接收芯片,實現DVB-ASI信號的接收。

關鍵

- 關鍵字:

設計 接收 IP PCI 基于

- 回顧以太網同步技術的發展,我們曾在以太網上用過互聯網網絡時間協議NTP(Network Time Protocol)技術,簡單網絡時間協議SNTP(Simple Network Time Protocol)技術,GPS技術或用T1/E1和以太網組成混合網絡來增加以太網

- 關鍵字:

電信 特性 IP 確保 時鐘 同步 精確

- 近年來,模擬視頻監控系統的市場份額在不斷縮水,正如人們所期望的,IP視頻監控逐漸深入人心。確實,IP視頻監控解決了傳統監控布線繁瑣的問題,可是它也帶來了新的問題。 模擬攝像機達到650線便已是最高水平,然而

- 關鍵字:

選型 指導 存儲設備 監控系統 視頻 IP

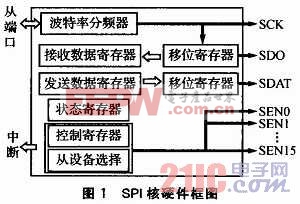

- 摘要:介紹了SPI總線控制器IP核的硬件結構與應用方法,并著重介紹了該IP核在微投影系統中的使用,以完成微顯示芯片的初始化。實驗表明,該SPI總線接口使用靈活,便于移植,并且穩定可靠。

關鍵詞:SPI總線控制器;N

- 關鍵字:

系統 應用 投影 及其 IP SPI

- 摘要:介紹了FreeARM7 IP核的基本概況及其接口特點,以LPC2101為原型對該IP核進行了擴展。結合USB 1.1設備控制器IP核和自定制硬件邏輯,構建了一種微控制器功能驗證回路。在主機端開發了驗證程序、驅動和通信軟件。

- 關鍵字:

擴展 驗證 邏輯 微處理器 IP FreeARM7

- 摘要:介紹了一種基于Wishbone總線的UART IP核的設計方法。該設計采用了自頂向下的模塊化劃分和有限狀態機相結合的方法,由于其應用了標準的Wishbone總線接口,從而使微機系統與串行設備之間的通信更加靈活方便。驗證

- 關鍵字:

IP 設計 UART 總線 Wishbone 基于

- 芯片設計愈趨復雜,對已驗證IP的需求也愈來愈高,根據全球半導體協會(GSA)統計,2010年晶圓代工廠提供給IC設計業者的IP數量,已經超過以IP授權為主要業務的第三方IP供貨商。為了縮短芯片設計至量產時間,臺積電旗下創意、聯電旗下智原等2家設計服務業者,已經成為晶圓雙雄搶食IP授權市場趨勢下的主要受惠者。

根據GSA調查統計,IC設計業者的IP來源,雖然因為芯片設計功能區塊(design block)仍以自家技術為主,自有IP比例達到66%,但是去年一年當中,已有愈來愈多的IC設計業者開始依賴

- 關鍵字:

臺積電 IP

all-ip介紹

您好,目前還沒有人創建詞條all-ip!

歡迎您創建該詞條,闡述對all-ip的理解,并與今后在此搜索all-ip的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473