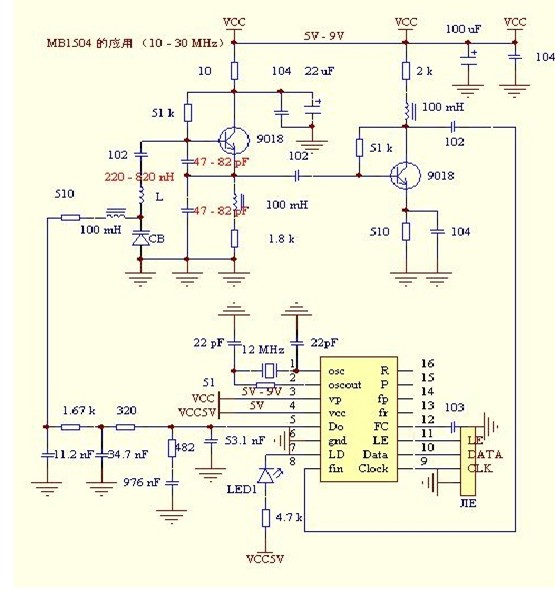

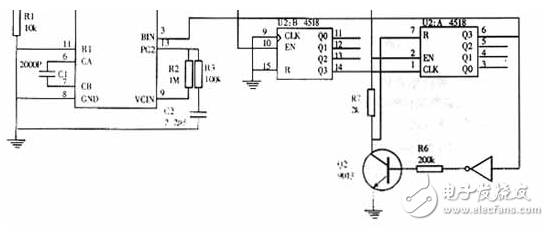

- 摘要:為了解決車輛計數問題,將環形線圈作為傳感器,鋪設在公路行車道上。當車輛通過線圈上面時,由于電感L發生變化,引起振蕩電路的頻率發生變化;通過鎖相環芯片檢測頻率的變化,使模擬信號轉化成數字信號,將鎖相

- 關鍵字:

車流量檢測 環形線圈 振蕩電路 鎖相環

- 摘要: 介紹了鎖相環的原理以及Freescale 公司的鎖相環頻率合成器件MC145151- 2 的主要特點,給出了MC145151- 2 和ICL8038 低頻鎖相環函數發生器的工作原理、設計思想、電路結構、模塊設計方法及其電路原理圖。1 引言

- 關鍵字:

鎖相環 低頻 函數發生器

- 小數N分頻PLL從上世紀七十年代開始就已投入使用。小數N分頻使PLL輸出的分辨率可以降至PFD頻率的一小部分(如圖所示),其中PFD輸入頻率為1 MHz。可以產生分辨率為數百Hz的輸出頻率,同時維持較高的PFD頻率。因此,小數

- 關鍵字:

小數N分頻 鎖相環 分析

- 圖3.24給出了CADILLAC時鐘相位調整電路的框圖。對于大規模生產測試,可能值得構造這樣的電路。對于普通的實驗測試,則太麻煩了。電路將總線時鐘進行N分頻,然后通過一個-頻率比較器把它與一個同樣經過N分頻的本地振蕩

- 關鍵字:

鎖相環 時間調整 分析

- 1 引言數字鎖相環路已在數字通信、無線電電子學及電力系統自動化等領域中得到了極為廣泛的應用。隨著集成電路技術的發展,不僅能夠制成頻率較高的單片集成鎖相環路,而且可以把整個系統集成到一個芯片上去。在基于FP

- 關鍵字:

FPGA 全數字 鎖相環

- 本文介紹了一種基于CMOS工藝的高性能處理器時鐘系統設計,設計頻率為200MHz,VCO的相位噪聲為-110dBC/Hz@100kHz ...

- 關鍵字:

鎖相環 時鐘系統 壓控振蕩器

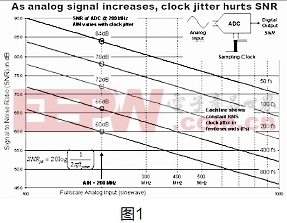

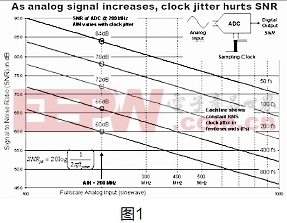

- 摘要:本文根據光纖接入數字中頻系統的時鐘使用情況,分析了時鐘抖動對ADC和鎖相環性能影響的原理,講述了鎖相環的基本原理和相噪優化方式,最后給出采用雙環鎖相環來完成去抖和時鐘分發的解決方案。

- 關鍵字:

時鐘抖動 鎖相環 201204

- 摘要:介紹了新型數字視頻接口的發展背景和技術優勢,詳細分析了DVI1.0的通信協議、T.M.D.S.的鏈路構成、信號特性、編碼及解...

- 關鍵字:

數字視頻接 差分信號 信號編碼 鎖相環

- 高頻鎖相環的可測性設計可測性設計(Design for Test,DFT)最早用于數字電路設計。隨著模擬電路的發展和芯片 集 ...

- 關鍵字:

高頻 鎖相環 可測性

- 電路功能與優勢 該電路是低噪聲微波小數N分頻PLL的完整實現方案,以 ADF4156 作為核心的小數N分頻PLL器件 ...

- 關鍵字:

低噪聲 N分頻 鎖相環

- 摘要:介紹一種基于ADμC842單片機的激光波長計信號采集系統,該系統采用ADμC842外部觸發DMA工作方式,實現對待 ...

- 關鍵字:

波長計 單片機 DMA 鎖相環

- 該應用筆記討論了鑒頻鑒相器的指標對鎖相環(PLL)死區及抖動性能的影響。在使用電荷泵環路濾波的PLL設計中,通...

- 關鍵字:

鑒相器 鎖相環

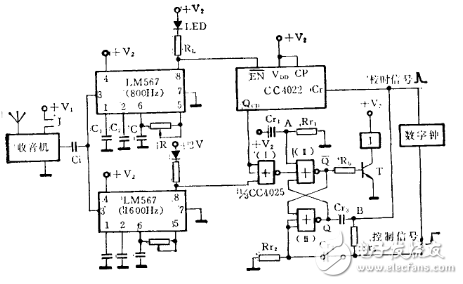

- 1.鎖相環的基本組成許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實現這個目的。

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL)。鎖相環的特點是:利用外部輸入的參

- 關鍵字:

鎖相環 工作原理

鎖相環介紹

能使受控振蕩器的頻率和相位均與輸入信號保持確定關系的閉環電子電路。鎖相環的基本結構如圖1,其中鑒相器用來鑒別輸入信號ui與輸出信號u0之間的相位差,并輸出誤差電壓ud。ud中的噪聲和干擾成分被低通性質的環路濾波器濾除,形成壓控振蕩器(VCO)的控制電壓uC。uC作用于壓控振蕩器的結果是把它的輸出振蕩頻率f0拉向環路輸入信號頻率fi,當二者相等時,環路被鎖定,稱為入鎖。維持鎖定的直流控制電壓由鑒相器 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473