高頻鎖相環的可測性設計

可測性設計(Design for Test,DFT)最早用于數字電路設計。隨著模擬電路的發展和芯片 集成度的提高,單芯片數模混合系統應運而生,混合電路測試,尤其是混合電路中模擬電路的測試,引起了設計者的廣泛關注。邊界掃描是數字電路可測性設計中常用的技術,基于IE EE1149?1邊界掃描技術。本文針對一款應用于大規模集成電路的CMOS高頻鎖相環時鐘發生器,提出了一種可行的測試方案,重點講述了鎖相環的輸出頻率和鎖定時間參數的測試,給出了具體的測試電路和測試方法。對于應用在大規模電路系統中的鎖相環模塊,該測試方案既可用于鎖相環的性能評測,也可用于鎖相環的生產測試。?

1 鎖相環結構及原理

本文所要測試的是用于大規模集成電路的鎖相環時鐘發生器,他是一款基于0.18 μm CMOS 數字工藝設計的高頻電荷泵鎖相環(Charge Pump Phase Locking Loop,CPPLL),最高輸出頻率達1.2 GHz。

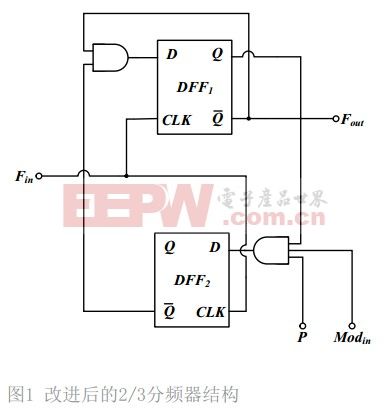

此鎖相環的電路結構如圖1所示,他包括輸入分頻器、鑒頻鑒相器(Phase Freq

為了更好地抑制噪聲,鎖相環采用了差分的電路結構。其中,壓控振蕩器采用環形振蕩器結 構實現,主要由3個完全相同的延遲單元順次連接而成。

2 測試方案

模擬電路傳統的測試方法比較簡單,將輸入輸出信號直接引出,檢測輸入信號對應的輸出響 應即可。隨著工作頻率的升高,封裝管腳和引線寄生參數不容忽視,傳統的測試方法也受到挑戰。由于模擬信號的抗干擾能力差,輕微的擾動都可能會影響電路的性能,測試電路應該盡量簡單,以避免引入不必要的噪聲。

最高輸出頻率、輸出頻率范圍和鎖定時間等都是高頻鎖相環需要測試的重要性能參數。對于工作頻率高達GHz的高頻鎖相環,顯然難以采用傳統的測試方法來完成,需要進行專用測試電路設計,即在芯片內設計一定的測試電路以便投片后進行測試。

2.1 輸出頻率測試

作為時鐘發生器,鎖相環一般工作于整個電路系統的最高頻率,而壓控振蕩器工作于鎖相環的最高頻率。如圖1所示,鎖相環的輸出頻率就是壓控振蕩器的工作頻率,因此鎖相環的輸出頻率測試實質上是對壓控振蕩器的最高振蕩頻率和振蕩范圍的測試。

由于輸出管腳的引線存在寄生的電感電容,這些寄生參數容易引入較大的高頻耦合噪聲;高頻信號經過這些引線輸出到管腳通常會產生較大的衰減。因此,壓控振蕩器的高頻輸出信號很難引出芯片外直接測量。另一方面,高頻信號的測試對測量儀器要求很高,測試板上的外加信號一旦經過高頻通路耦合到電路內部,就會影響測試結果,甚至干擾電路的工作。

<

評論