電路 文章 最新資訊

亞微米CMOS電路中VDD-VSSESD保護結構設計(二)

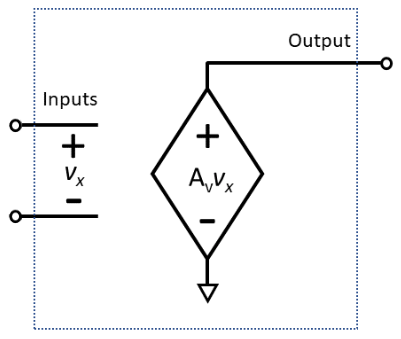

- 3 仿真分析及具體設計結果3.1 仿真分析在亞微米的ESD結構的設計中,一種常見的具體的ESD瞬態檢測電壓如圖2 VDD-VSS間的電壓鉗位結構。其原理如下:主要利用結構中的RC延遲作用,一般T=RC被設計為100ns-1000ns之間,而

- 關鍵字: VDD-VSSESD CMOS 亞微米 電路

亞微米CMOS電路中VDD-VSSESD保護結構設計

- 1 引言ESD(Electric Static Discharge)保護結構的有效設計是CMOS集成電路可靠性設計的重要任務之一,其ESD結構與工藝技術、特征尺寸密切相關,隨著IC工藝技術的進一步發展,特征尺寸越來越小,管子的柵氧層厚度越來越

- 關鍵字: VDD-VSSESD CMOS 亞微米 電路

電路介紹

type D conditioning

D型調節,D型修整(話音級電路)

type D conditioning

[ 查看詳細 ]

熱門主題

電路設計

驅動電路

邏輯電路

印制電路

模擬電路

降壓電路DC/DC

數字電路

數字/模擬混合電路系統

模擬集成電路

射頻電路

電路圖

監控電路

IC電路板測試

印制電路板

印刷電路板

電路保護

電子設計.集成電路

集成電路設計

印刷電路

保護電路

Buck-Boost電路

DC/DC電路

控制電路

開關電路

柔性電路板

PC-DSP通信電路

“555”電路

集成電路(IC)卡

FM/AM收音機集成電路

高密度(HD)電路

專用集成電路(ASIC)

集成電路

雙音多頻(DTMF)編碼式遙控電路

AC-DC開關電源電路特征

集成電路(IC)

印刷電路板(PCB)

射頻(RF)電路

印制電路板(PCB)

高密度印制電路板(HDI)

北歐集成電路公司(NORDIC)

厚膜混合集成電路(HIC)技術

數字邏輯電路

樹莓派

linux