- 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些小技巧和幫助來設置時鐘;使用像Synopsys Synplify Premier一樣的工具正確地設置時序約束;然后調整參數使之滿足賽靈思FPGA設計性能的目標。

會有來自不同角度的挑戰,包括:

● 更好的設計計劃,例如完整的和精確的時序約束和時鐘規范

● 節約時間的設計技術,例如為更好的性能結

- 關鍵字:

FPGA Synplify 時序

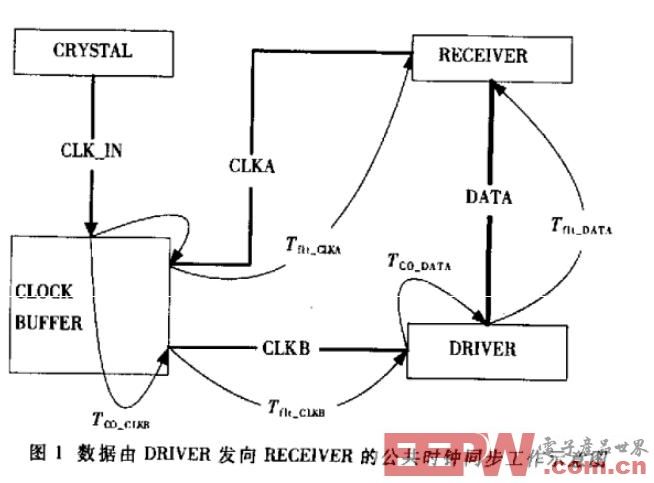

- 在網絡通訊領域,ATM交換機、核心路由器、千兆以太網以及各種網關設備中,系統數據速率、時鐘速率不斷提高,相應處理器的工作頻率也越來越高;數據、語音、圖像的傳輸速度已經遠遠高于500Mbps,數百兆乃至數吉的背板也越來越普遍。數字系統速度的提高意味著信號的升降時間盡可能短,由數字信號頻率和邊沿速率提高而產生的一系列高速設計問題也變得越來越突出。當信號的互連延遲大于邊沿信號翻轉時間的20%時,板上的信號導線就會呈現出傳輸線效應,這樣的設計就成為高速設計。高速問題的出現給硬件設計帶來了更大的挑戰,有許多從邏

- 關鍵字:

PCB 時鐘 時序

- 規范很重要

工作過的朋友肯定知道,公司里是很強調規范的,特別是對于大的設計(無論軟件還是硬件),不按照規范走幾乎是不可實現的。邏輯設計也是這樣:如果不按規范做的話,過一個月后調試時發現有錯,回頭再看自己寫的代碼,估計很多信號功能都忘了,更不要說檢錯了;如果一個項目做了一半一個人走了,接班的估計得從頭開始設計;如果需要在原來的版本基礎上增加新功能,很可能也得從頭來過,很難做到設計的可重用性。

在邏輯方面,我覺得比較重要的規范有這些:

1.設計必須文檔化。要將設計思路,詳細實現等寫入文檔

- 關鍵字:

FPGA 時序 電路

- 時序的由來我們已經知道單片機執行指令的過程就是順序地從ROM程序存儲器中取出指令一條一條的順序執行然后 ...

- 關鍵字:

單片機 時序 周期

- 51單片機時序及延時分析計算機工作時,是在統一的時鐘脈沖控制下一拍一拍地進行的。這個脈沖是由單片機控制 ...

- 關鍵字:

51單片機 時序 延時分析

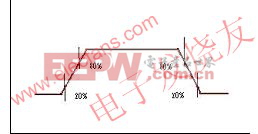

- 由于工程師們都在竭盡所能地獲得其電源的最高效率,時序優化正變得越來越重要。在開關期間,存在兩個過渡階段:低...

- 關鍵字:

電源設計 同步降壓 FET 時序

- 由于火箭炮發射的是簡易控制火箭彈,因此其定向管與火箭彈之間的電氣信號接口除了與普通無控火箭彈一樣具有點火信號接口外,還另有一個32芯參數裝定信號接口。在發射程序中,如果火控系統計算的火箭彈的飛行控制參數

- 關鍵字:

檢測系統 設計 時序 單片機 MSP430F149 基于

- 摘要:設計了一種用于OTP存儲器的片上時序信號產生電路。由地址變化探測電路和脈沖寬度調整電路組成。地址變化檢測電路檢測地址信號的變化,再由脈沖寬度調整電路產生一個寬度適中的時序信號,用于內部時序控制。其具

- 關鍵字:

OTP 存儲器 時序 信號產生電路

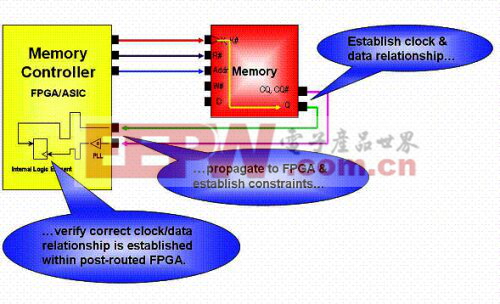

- 如何有效的管理FPGA設計中的時序問題, 當

二、導言 FPGA的設計與高速接口技術可以幫助你滿足今天的市場要求,但也提出了一些有趣的設計挑戰。為了確保存儲器接口的數據傳輸準確,在超過200兆赫茲以上,進行時序分析將發揮更突出的作用,以

- 關鍵字:

時序 問題 設計 FPGA 有效 管理 如何

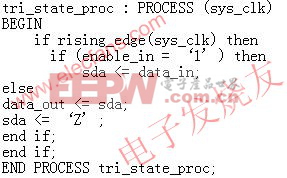

- FPGA時序收斂分析,您編寫的代碼是不是雖然在仿真器中表現正常,但是在現場卻斷斷續續出錯?要不然就是有可能在您使用更高版本的工具鏈進行編譯時,它開始出錯。您檢查自己的測試平臺,并確認測試已經做到 100% 的完全覆蓋,而且所有測試

- 關鍵字:

分析 收斂 時序 FPGA

- 單片機內部的時序

單片機執行各種操作時,CPU都是嚴格按照規定的時間順序完成相關的工作,這種時間上的先后順序成為時序。

單周期指令的操作時序

雙周期指令的操作時序

時鐘電路

時鐘電路參數:

頻

- 關鍵字:

分析 時序 內部 單片機

- 單片機內部的時序 單片機執行各種操作時,CPU都是嚴格按照規定的時間順序完成相關的工作,這種時間上的先后順序成為時序。

單周期指令的操作時序

雙周期指令的操作時序

時鐘電路

時鐘電路參數:

頻率

- 關鍵字:

簡介 時序 內部 單片機

- 為了避免同步RS觸發器的輸入信號同時為1,可以在S和R之間接一個“非門”,信號只從S端輸入,并將S端改稱為數據輸入端D,如圖15-8所示。這種單輸入的觸發器稱為同步D觸發器,也稱D鎖存器。

由圖可知,S=D,

- 關鍵字:

D觸發器 時序 原理

- SOC時序分析中的跳變點介紹, 跳變點是所有重要時序分析工具中的一個重要概念。跳變點被時序分析工具用來計算設計節點上的時延與過渡值。跳變點的有些不同含義可能會被時序分析工程師忽略。而這在SOC設計后期,也就是要對時序簽字時可能會導致問

- 關鍵字:

介紹 分析 時序 SOC

- 現今,電子系統往往具有許多不同的電源軌。在采用模擬電路和微處理器、DSP、ASIC、FPGA的系統中,尤其如此。為實現可靠、可重復的操作,必須監控各電源電壓的開關時序、上升和下降速率、加電順序以及幅度。既定的電源

- 關鍵字:

控制 時序 監控 系統 電源

時序介紹

您好,目前還沒有人創建詞條時序!

歡迎您創建該詞條,闡述對時序的理解,并與今后在此搜索時序的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473