- 時鐘分頻在之前的實驗中我們已經熟悉了小腳丫的各種外設,掌握了verilog的組合邏輯設計,接下來我們將學習時序邏輯的設計。====硬件說明====時鐘信號的處理是FPGA的特色之一,因此分頻器也是FPGA設計中使用頻率非常高的基本設計之一。一般在FPGA中都有集成的鎖相環可以實現各種時鐘的分頻和倍頻設計,但是通過語言設計進行時鐘分頻是最基本的訓練,在對時鐘要求不高的設計時也能節省鎖相環資源。在本實驗中我們將實現任意整數的分頻器,分頻的時鐘保持50%占空比。1,偶數分頻:偶數倍分頻相對簡單,比較容易理解。通

- 關鍵字:

時序邏輯 時鐘分頻 FPGA Lattice Diamond 小腳丫

- 時鐘分頻在之前的實驗中我們已經熟悉了小腳丫的各種外設,掌握了verilog的組合邏輯設計,接下來我們將學習時序邏輯的設計。硬件說明時鐘信號的處理是FPGA的特色之一,因此分頻器也是FPGA設計中使用頻率非常高的基本設計之一。一般在FPGA中都有集成的鎖相環可以實現各種時鐘的分頻和倍頻設計,但是通過語言設計進行時鐘分頻是最基本的訓練,在對時鐘要求不高的設計時也能節省鎖相環資源。在本實驗中我們將實現任意整數的分頻器,分頻的時鐘保持50%占空比。1,偶數分頻:偶數倍分頻相對簡單,比較容易理解。通過計數器計數是完

- 關鍵字:

時序邏輯 時鐘分頻 FPGA Lattice Diamond 小腳丫

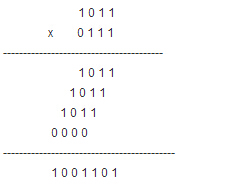

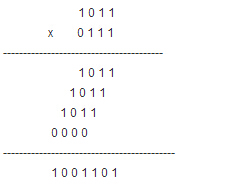

- 上次看了一下關于乘法器的Verilog代碼,有幾個地方一直很迷惑,相信很多初學者看這段代碼一定跟我當初一樣,看得一頭霧水,在網上也有一些網友提問,說這段代碼不好理解,今天小墨同學就和大家一起來看一下這段代碼,我會親自在草稿紙上演算,盡量把過程寫的詳細些,讓更多的人了解乘法器的設計思路。

下面是一段16位乘法器的代碼,大家可以先瀏覽一下,之后我再做詳細解釋

module mux16(

clk,rst_n,

start,ain,bin,yout,done

);

inpu

- 關鍵字:

FPGA Verilog 時序邏輯

- 寄存器傳輸級(RTL)驗證在數字硬件設計中仍是瓶頸。行業調研顯示,功能驗證占整個設計工作的70%。但即使把重點放在驗證上面,仍有超過60%的設計出帶需要返工。其主要原因是在功能驗證過程中暴露出來的邏輯或功能瑕疵和

- 關鍵字:

RTL 時序邏輯 等效 檢查方法

- 寄存器傳輸級(RTL)驗證在數字硬件設計中仍是瓶頸。行業調研顯示,功能驗證占整個設計工作的70%。但即使把重點放在驗證上面,仍有超過60%的設計出帶需要返工。其主要原因是在功能驗證過程中暴露出來的邏輯或功能瑕疵和

- 關鍵字:

時序邏輯 等效 檢查方法 風險

時序邏輯介紹

時序邏輯 由多個觸發器和多個組合邏輯塊組成的網絡。常用的有:計數器、復雜的數據流動控制邏輯、運算控制邏輯、指令分析和操作控制邏輯。同步時序邏輯是設計復雜的數字邏輯系統的核心。時序邏輯借助于狀態寄存器記住它目前所處的狀態。在不同的狀態下,即使所有的輸入都相同,其輸出也不一定相同。 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473