- 電路的功能穩定度好的基準電壓應用范圍很廣,它涉及到所有的模擬電路。本電路采用了產生基準電壓。當然也可用普通齊納二極管代替專用IC。可以說這是具有通用性的基準電壓發生器。電路工作原理OP放大器采用單一電源,

- 關鍵字:

功能 原理 介紹 電路 發生 10V 基準 電壓 2.5

- 電路的功能產生基準電壓用的二極管,如果采用溫度補償式,就須加大偏流,如NEC公司的IS2190系列產品,必須有10MA的偏流,該偏流不是由電源供給的,而是由輸出端供給的,這樣即使電源變動,也能保證穩定工作,另外因為

- 關鍵字:

發生 電路 功能 原理 電壓 基準 補償 齊納 二極管 10V

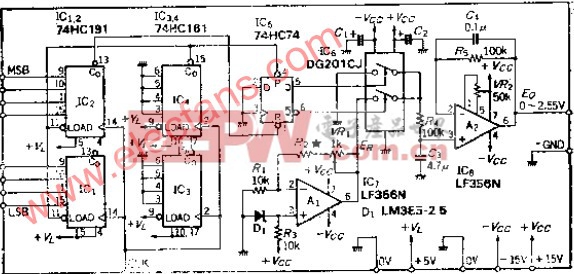

- 電路的功能這種PWM式的D-A轉換器,數據范圍為0~255(8位二進制),因此能以10MV為一步,產生0~2.55V的電壓另外通過改變電阻R2可使滿量程電壓在10V以內隨意設定。電壓變化取決于脈沖占空比,因此,只要基準電壓穩定,

- 關鍵字:

電壓 功能 原理 分析 電路 基準 準確 PWM 步進 發生

- 目前,基準電壓源被廣泛應用與高精度比較器,A/D,D/A轉換器,動態隨機存儲器等集成電路中。基準電壓源是集成電路中一個重要的單元模塊。它產生的基準電壓精度,溫度穩定性和抗噪聲干擾能力直接影響到芯片,甚至整個

- 關鍵字:

基準 技術 介紹 電壓 設計 Pipeline ADC 14位

- 本文采用一種低電壓帶隙基準結構。在TSMC0.13mu;m CMOS工藝條件下完成,包括核心電路、運算放大器、偏置及啟動電路的設計,并用Cadence Spectre對電路進行了仿真驗證。基準電壓是數模混合電路設計中一個不可缺少的

- 關鍵字:

電壓 方法 設計 基準 供電 電路

- 在要求絕對測量的應用場合,其準確度受使用基準值的準確度的限制。但是在許多系統中穩定性和重復性比絕對精度更重要;而在有些數據采集系統中電壓基準的長期準確度幾乎完全不重要,但是如果從有噪聲的系統電源中派生基

- 關鍵字:

設計 電壓 基準 精密

- 摘要:為了滿足深亞微米級集成電路對低溫漂、低功耗電源電壓的需求,提出了一種在0.25mu;m N阱CMOS工藝下,采用一階溫度補償技術設計的CMOS帶隙基準電壓源電路。電路核心部分由雙極晶體管構成,實現了VBE和VT的線性

- 關鍵字:

研究 電壓 基準 CMOS 低溫

- 通常我們選用穩壓二極管作為基準電壓源,這是最簡單、也是最傳統的方法,按照所需電壓值選一個對應型號的穩壓管當然可以,但選得是否合適、是否最佳,卻大有講究。 最基本的電壓基準源電路如圖1(a)、穩壓管的擊穿

- 關鍵字:

介紹 選用 設計 電壓 基準

- 摘要:本文針對傳統基準電壓的低PSR以及低輸出電壓的問題,通過采用LDO與帶隙基準的混合設計,并且采用BCD工藝,得到了一種可以輸出較高參考電壓的高PSR(電源抑制)帶隙基準。此帶隙基準的1.186 V輸出電壓在低頻時PSR

- 關鍵字:

實現 基準 PSR

- 1 引 言 隨著各種便攜式移動通信和計算產品的普及,對電池的需求大大加強,但是電池技術發展相對落后,降低電路的功耗成為IC設計關注的一個焦點;電路的功耗會全部轉換成熱能,過多的熱量會產生焦耳熱效應,加劇硅

- 關鍵字:

基準 設計 電壓 電流 消耗 380nA 最大

- 摘要 設計了一款帶隙基準電壓源,基于0.18mu;m的CMOS工藝,在Hspice下仿真,仿真結果表明,溫度在-25~80℃內變化時,溫度系數為9.14times;10-6℃;電源電壓在3~5 V之間變化時,基準電壓在1 250plusmn;43 mV內

- 關鍵字:

仿真 設計 電壓 基準

- 摘要:文章基于CMOS 0.18mu;m工藝,在Hspice下,對四利PMOS管基準電壓源進行了分析和仿真,文中給出了每種電路仿真時的電路參數和仿真結果。

關鍵詞:基準電壓;CMOS集成電路;Hspice

0 引言

模擬電路廣泛

- 關鍵字:

仿真 分析 電壓 基準 CMOS

- 但是,由于本設計采用LDO供電,而LDO的參考電壓是bg,存在死循環,即bg低,則LDO低,所以基準核心的VQC5無法給VQCS2提供電流,也就無法提高VQC2的電壓即bg,因此需要外界提供大電流bias-start,使得當LDO無法啟動基

- 關鍵字:

方案 設計 基準 抑制 電源

- 摘要:本文針對傳統基準電壓的低PSR以及低輸出電壓的問題,通過采用LDO與帶隙基準的混合設計,并且采用BCD工藝,得到了一種可以輸出較高參考電壓的高PSR(電源抑制)帶隙基準。此帶隙基準的1.186 V輸出電壓在低頻時PS

- 關鍵字:

設計 基準 抑制 電源

- 基準電壓源可廣泛應用于A/D、D/A轉換器、隨機動態存儲器、閃存以及系統集成芯片中。使用0.18 μm CMOS工藝設計了具有高穩定度、低溫漂、低輸出電壓為0.6 V的CMOS基準電壓源。

- 關鍵字:

設計 電壓 基準 CMOS 0.18

基準介紹

您好,目前還沒有人創建詞條基準!

歡迎您創建該詞條,闡述對基準的理解,并與今后在此搜索基準的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473