一種低溫漂的CMOS帶隙基準電壓源的研究

摘要:為了滿足深亞微米級集成電路對低溫漂、低功耗電源電壓的需求,提出了一種在0.25μm N阱CMOS工藝下,采用一階溫度補償技術設計的CMOS帶隙基準電壓源電路。電路核心部分由雙極晶體管構成,實現了VBE和VT的線性疊加,獲得近似零溫度系數的輸出電壓。T—SPICE軟件仿真表明,在3.3 V電源電壓下,當溫度在-20~70℃之間變化時,該電路輸出電壓的溫度系數為10x10-6/℃,輸出電壓的標準偏差為1 mV,室溫時電路的功耗為5.283 1 mW,屬于低溫漂、低功耗的基準電壓源。

關鍵詞:帶隙參考電壓源;溫度補償;電源抑制比

近年來,由于集成電路的飛速發展,基準電壓源在模擬集成電路、數模混合電路以及系統集成芯片(SOC)中都有著非常廣泛的應用,對高新模擬電子技術的應用和發展也起著至關重要的作用,其精度和穩定性會直接影響整個系統的性能。因此,設計一個好的基準源具有十分現實的意義。

1 帶隙基準電路的基本原理

帶隙基準電壓源的目的是產生一個對溫度變化保持恒定的量,由于雙極型晶體管的基極電壓VBE,其溫度系數在室溫(300 K)時大約為-2.2 mV/K,而2個具有不同電流密度的雙極型晶體管的基極-發射極電壓差VT,在室溫時的溫度系數為+0.086 mV/K,由于VT與VBE的電壓溫度系數相反,將其乘以合適的系數后,再與前者進行加權,從而在一定范圍內抵消VBE的溫度漂移特性,得到近似零溫度漂移的輸出電壓VREF,這是帶隙電壓源的基本設計思想。

1.1 帶隙基準電壓源核心電路

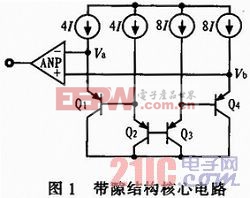

本文提出的電路核心結構如圖1所示,在電路中雙極晶體管構成了電路的核心,實現了VBE與VT的線性疊加,獲得近似為零溫度系數的輸出電壓。圖1中雙極型晶體管Q1和Q2的發射區面積相同,Q3和Q4的發射區面積相同,考慮設計需求,取Q1和Q2的發射區面積為Q3和Q4的發射區面積的8倍。

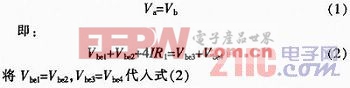

假設雙極晶體管基極電流為零,運放的增益足夠大,則a點和b點的電壓相等,即:

在實際電路中,經過計算可知當取R3/R1=2.3066時,可以得到室溫下的近似零溫度系數的輸出參考電壓。

評論