基于多數(shù)決定邏輯門的全加器電路設(shè)計

O 引言

加法運算是算術(shù)運算中最基本的運算。減法、乘法、除法及地址計算這些基于加法的運算已廣泛地應(yīng)用于超大規(guī)模集成電路(VLSI)中。全加器是組成二進制加法器的基本組成單元,所以提高全加器的性能是提高運算器性能的最重要途徑之一。

對于全加器結(jié)構(gòu)的研究,國內(nèi)外有許多相關(guān)報道,大多數(shù)研究致力于提高全加器的速度和降低其功耗。設(shè)計全加器的方法有很多種,最簡單的方法是用組合門實現(xiàn)所需的邏輯函數(shù),另外一種常用的方法是采用傳輸門實現(xiàn)。由于傳輸門具有很強的邏輯功能,且輸入電容小,因而用傳輸門實現(xiàn)的全加器速度快,且結(jié)構(gòu)簡單。采用傳輸門實現(xiàn)的全加器比組合門實現(xiàn)的全加器電路要簡單。但這種電路以CMOS傳輸門為基本單元,而不是在管子級進行設(shè)計,因而,這種全加器電路存在冗余,需進一步簡化。

結(jié)合上面的討論,提出一種結(jié)構(gòu)更加簡單,性能更好的加法器單元電路,它僅由輸入電容和CMOS反向器組成,而且通過電路簡化設(shè)計,克服了功耗問題。

本文首先提出多數(shù)決定邏輯門的概念和電路設(shè)計,然后提出了一種基于多數(shù)決定邏輯門的全加器電路設(shè)計。該全加器三個主要特征是較少的管子、工作于極低電源電壓以及短路電流的消除。模擬結(jié)果表明,這種新的結(jié)構(gòu)能夠很好地完成全加器的邏輯功能。

1 多數(shù)決定邏輯非

1.1 多數(shù)決定邏輯非的提出

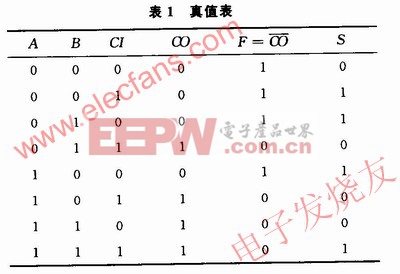

多數(shù)決定邏輯(Majority Logic)定義為:若邏輯1的個數(shù)大于邏輯0的個數(shù),則輸出為邏輯1;若邏輯O的個數(shù)大于邏輯1的個數(shù),則輸出為邏輯O。表1中CO即為A,B,CI的多數(shù)決定邏輯,邏輯式表示為CO=M(A,B,CI)。多數(shù)決定邏輯非(Majority-not Logic)則為多數(shù)決定邏輯非函數(shù),表1中![]() 即為A,B,CI的多數(shù)決定邏輯非函數(shù),邏輯式表示為F=F(A,B,CI)。

即為A,B,CI的多數(shù)決定邏輯非函數(shù),邏輯式表示為F=F(A,B,CI)。

1.2 多數(shù)決定邏輯非門的電路設(shè)計

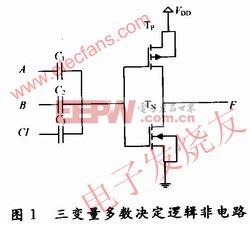

圖1即為三輸入端的多數(shù)決定邏輯非門電路。其中,C1=C2=C3,它由輸入電容和一個靜態(tài)CMOS反向器構(gòu)成。只需增加輸入電容的個數(shù),即可增加輸入端的個數(shù)。電容網(wǎng)絡(luò)的作用是分離電壓。當(dāng)輸入端中O的個數(shù)多于l的個數(shù),電容網(wǎng)絡(luò)的輸出為0,經(jīng)反向器之后輸出為高電平1(VDD);當(dāng)輸入端中1的個數(shù)多于0的個數(shù),電容網(wǎng)絡(luò)的輸出為1,經(jīng)反相器之后輸出為低電平O(0 V)。輸入電容的電容值大約為O.05 fF,它對電路沒有影響。歡迎轉(zhuǎn)載,本文來自電子發(fā)燒友網(wǎng)(http://www.elecfans.com/)

輸入電容可選擇用金屬氧化物半導(dǎo)體(MOS)電容。與其他電容相比,MOS電容具有占用芯片面積小,電容值大,更容易匹配等優(yōu)點。一個MOS電容所占用芯片的面積與一個普通晶體管相當(dāng)。通常,對于相同的面積,PMOS電容值大于NMOS電容值。所以可選用PMOS電容來實現(xiàn)多數(shù)決定邏輯非門的輸入電容。

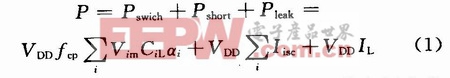

普通CMOS門電路的功耗主要由動態(tài)功耗Pswich、短路功耗Pshort、靜態(tài)漏電流功耗Pleak三部分組成,見式(1)。如果滿足式(2),則兩個管子不能同時導(dǎo)通,除去Pshort,功耗將顯著減小。

式中:fcp表示系統(tǒng)時鐘脈沖;Vim為節(jié)點i的電壓變化范圍(理想情況下為VDD);CiL為節(jié)點i的等效負載電容;ai為節(jié)點i的活動因子;Iisc和IL分別為短路電流和漏電流;P為總功耗。![]()

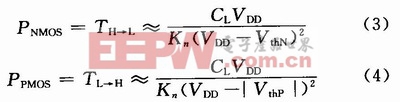

式中:VthP和VthN分別是PMOS管和CMOS管的開啟電壓。開啟電壓指的是絕緣柵場效應(yīng)管(MOSFET)溝道形成時的電壓。

圖1中因為電路僅用了兩個管子,所以電源電壓可減小,相對于電源電壓,Pswich將以二次方的速度衰減。只需滿足式(2),除去Pshort。所以其功耗大大小于傳統(tǒng)的CMOS門電路。

雖然減小電源電壓可以減小功耗,但是會影響電路的輸出波形。式(3)、式(4)給出電源電壓的減小和開啟電壓的增大對管子高低電平轉(zhuǎn)換延遲時間的影響。

2 全加器的設(shè)計

2.1 全加器的邏輯設(shè)計

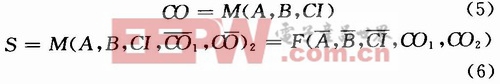

根據(jù)全加器的定義,其真值表如表1所示。其中,A和B為加數(shù)和被加數(shù),CI為來自低位的進位;S為和輸出,CO為進位輸出。根據(jù)前面的分析,全加器的進位輸出CO可表示為輸入A,B,CI的多數(shù)決定邏輯,而和輸出S則為A,B,CI,![]() ,

,![]() 五變量的多數(shù)決定邏輯,或表示為

五變量的多數(shù)決定邏輯,或表示為![]() ,CO1,CO2(其中CO=CO1,=CO2)的多數(shù)決定邏輯非。可用邏輯式表示出來:

,CO1,CO2(其中CO=CO1,=CO2)的多數(shù)決定邏輯非。可用邏輯式表示出來:

2.2 全加器的電路設(shè)計

根據(jù)邏輯式(5)、式(6),設(shè)計電路如圖2所示。該設(shè)計中,僅用了兩個多數(shù)決定邏輯非門。只需6個MOSFET即可實現(xiàn)優(yōu)化的CMOS全加器,用PSpice進行了晶體管級模擬。結(jié)果顯示,這種新的全加器能正確完成加法器的邏輯功能。圖2中,C1=C2=C3=0.05 fF,2C4=C5=C6=C7=2.88 fF。

DIY機械鍵盤相關(guān)社區(qū):機械鍵盤DIY

電流傳感器相關(guān)文章:電流傳感器原理 電容相關(guān)文章:電容原理 電容傳感器相關(guān)文章:電容傳感器原理

評論