基于多數決定邏輯非門的低功耗全加器設計

O 引言

加法運算是算術運算中最基本的運算。減法、乘法、除法及地址計算這些基于加法的運算已廣泛地應用于超大規模集成電路(VLSI)中。全加器是組成二進制加法器的基本組成單元,所以提高全加器的性能是提高運算器性能的最重要途徑之一。

對于全加器結構的研究,國內外有許多相關報道,大多數研究致力于提高全加器的速度和降低其功耗。設計全加器的方法有很多種,最簡單的方法是用組合門實現所需的邏輯函數,另外一種常用的方法是采用傳輸門實現。由于傳輸門具有很強的邏輯功能,且輸入電容小,因而用傳輸門實現的全加器速度快,且結構簡單。采用傳輸門實現的全加器比組合門實現的全加器電路要簡單。但這種電路以CMOS傳輸門為基本單元,而不是在管子級進行設計,因而,這種全加器電路存在冗余,需進一步簡化。

結合上面的討論,提出一種結構更加簡單,性能更好的加法器單元電路,它僅由輸入電容和CMOS反向器組成,而且通過電路簡化設計,克服了功耗問題。

本文首先提出多數決定邏輯門的概念和電路設計,然后提出了一種基于多數決定邏輯門的全加器電路設計。該全加器三個主要特征是較少的管子、工作于極低電源電壓以及短路電流的消除。模擬結果表明,這種新的結構能夠很好地完成全加器的邏輯功能。

1 多數決定邏輯非

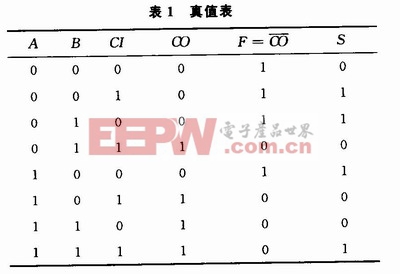

1.1 多數決定邏輯非的提出

多數決定邏輯(Majority Logic)定義為:若邏輯1的個數大于邏輯0的個數,則輸出為邏輯1;若邏輯O的個數大于邏輯1的個數,則輸出為邏輯O。表1中CO即為A,B,CI的多數決定邏輯,邏輯式表示為CO=M(A,B,CI)。多數決定邏輯非(Majority-not Logic)則為多數決定邏輯非函數,表1中![]() 即為A,B,CI的多數決定邏輯非函數,邏輯式表示為F=F(A,B,CI)。

即為A,B,CI的多數決定邏輯非函數,邏輯式表示為F=F(A,B,CI)。

1.2 多數決定邏輯非門的電路設計

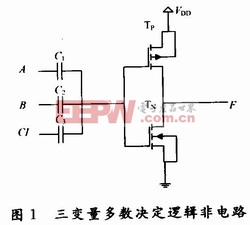

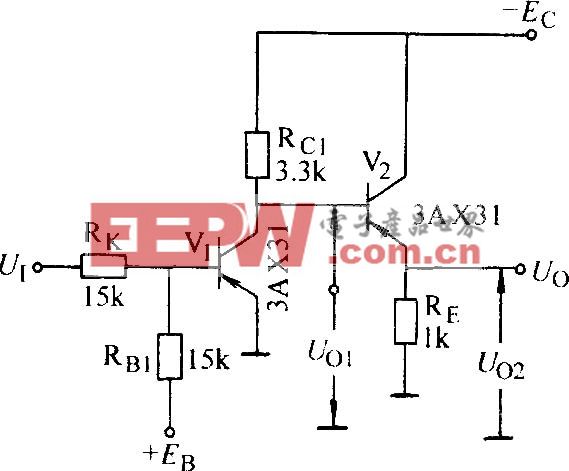

圖1即為三輸入端的多數決定邏輯非門電路。其中,C1=C2=C3,它由輸入電容和一個靜態CMOS反向器構成。只需增加輸入電容的個數,即可增加輸入端的個數。電容網絡的作用是分離電壓。當輸入端中O的個數多于l的個數,電容網絡的輸出為0,經反向器之后輸出為高電平1(VDD);當輸入端中1的個數多于0的個數,電容網絡的輸出為1,經反相器之后輸出為低電平O(0 V)。輸入電容的電容值大約為O.05 fF,它對電路沒有影響。

輸入電容可選擇用金屬氧化物半導體(MOS)電容。與其他電容相比,MOS電容具有占用芯片面積小,電容值大,更容易匹配等優點。一個MOS電容所占用芯片的面積與一個普通晶體管相當。通常,對于相同的面積,PMOS電容值大于NMOS電容值。所以可選用PMOS電容來實現多數決定邏輯非門的輸入電容。

評論