基于FPGA的多通道校準算法同步實現

表1為多通道校準算法的FPGA資源占用列表,從系統資源占用情況可以看出:多通道校準算法FPGA實現過程中,如果再加上前后端處理程序一起編譯,則輸入輸出端口將減少,資源占用也將減少,并不影響系統實現。其它各種資源占用量都較少,完全符合FPGA設計要求。

本文引用地址:http://www.104case.com/article/96056.htm

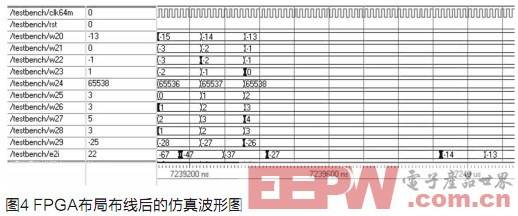

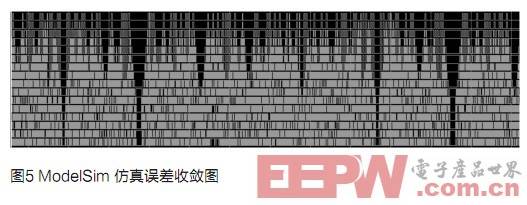

FPGA布局布線后的仿真波形如圖4、圖5所示。

從仿真結果(圖4,圖5)和ISE 8.2i的綜合報告可知,該校正模塊的最高時鐘頻率達到102.5MHz。

最后,由MATLAB仿真和FPGA布局布線后仿真得到的權值,經過MATLAB仿真形成新的方向圖,如圖6所示,可以看出,兩種方向圖基本一致。因此,基于FPGA的多通道校準同步算法的實現完全符合系統要求。

功分器相關文章:功分器原理

評論