多路可編程PWM芯片設計

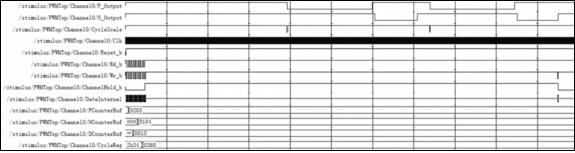

圖5 輸出結果與程序設定的周期和PWM波形完全一致

從圖5中,可以看到PWM輸出信號,在ClkGen的CycleScale信號的控制下周期輸出編程設定的PWM波形,并能異步響應ChannelHold_b信號的輸出控制。

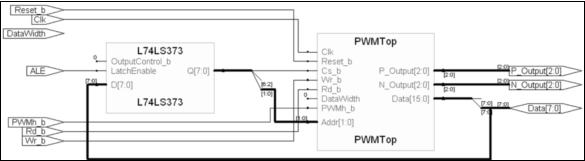

PWM的FPGA驗證,采用8bits數據接口,89c51[4]做外圍控制器(12MHz),對PWM進行操作。為了方便與單片機接口,將74LS373鎖存器內置到PWM中。整個數字設計部分見圖6。

圖6 PWM+L74LS373電路圖(與51單片機驗證)

通過Synplify Pro編譯后的結果顯示:

ProjectTopModule : PWMTopFor8051

Estimated Frequency: 72.9 MHz

Total LUTs: 1478 of 4160 (35%)

占用FPGA資源35%。針對51系列的單片機而言,PWM可運行的頻率遠超過系統頻率。因此在讀寫時序上可以完全保證整個設計的可靠性。

將編譯后的pof文件下載到APEX20KE EP20K100E TQ144-2X(Altera) fpga[5]驗證板。采用40MHz的FPGA時鐘。根據先前軟件仿真的步驟,將讀寫操作轉換為單片機程序燒錄到單片機。最后的結果通過示波器我們可以清楚的看到實際輸出與設計完全一致。芯片采用.35工藝,一次流片成功后,測試結果顯示結果非常理想,實現了當初的設計要求。

參考文獻:

[1] MICHAEL D. CILETTI著, 張雅綺, 李鏘等譯. Verilog HDL 高級數字設計[M]. 電子工業出版社 2005年

[2] 陸庭孝等著, 可靠性設計與分析[M]. 國防工業出版社, 1996年

[3] ModelSim Book Case, Mentor Graph 公司, 2006年

[4] 沈慶陽等著. 8051單片機實踐與應用[M]. 清華大學出版社, 2003年

[5] EDA先鋒工作室, 吳繼華, 王誠編著. Altera FPGA/CPLD 設計 (高級篇)[M]. 人民郵電出版社, 2005年

pwm相關文章:pwm是什么

pwm相關文章:pwm原理

脈寬調制相關文章:脈寬調制原理

評論