IGLOO─業(yè)界極低功耗的FPGA

(2) 更低的內(nèi)核電壓

本文引用地址:http://www.104case.com/article/92555.htmIGLOO的內(nèi)核可以支持1.2V或1.5V供電,1.2V的內(nèi)核電壓比1.5V的內(nèi)核電壓可以節(jié)省36%的動態(tài)功耗,可由公式1-1推導出,動態(tài)功耗與內(nèi)核電壓的平方成正比,所以1.2V的IGLOO系統(tǒng)比1.5V內(nèi)核電壓的系統(tǒng)可以節(jié)省更多的功耗,如圖5所示。

圖5 1.2V與1.5V系統(tǒng)的功耗對比

(3) 低功耗的Flash*Freeze模式

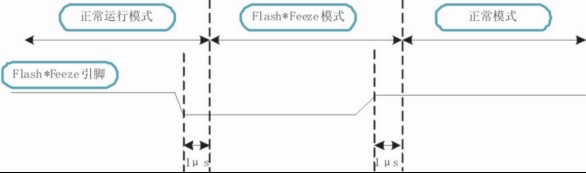

IGLOO具有一種獨特的Flash*Freeze模式,在這種模式下可以讓FPGA進入睡眠狀態(tài),在這種模式下最低的功耗可達2μW(IGLOO的Nano系列),并且能夠保存RAM和寄存器的狀態(tài),進入和退出這種模式只需要通過一個FPGA的Flash*Freeze引腳控制即可,進入和退出只需要1μs的時間,非常的方便,如圖6所示。

圖6 Flash*Freeze的操作模式

(4) 具有低功耗布局布線工具

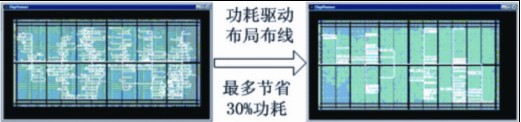

Actel提供免費的開發(fā)環(huán)境——Libero,并充分考慮了低功耗的設計,在軟件中增加了功耗驅(qū)動的布局布線,在該方式的驅(qū)動下,軟件自動以最低功耗的方式來布局并走線,類似于PCB繪制時的布局與走線,其中影響最大的是時鐘的走線,因為在大部分的設計中時鐘對功耗的影響起了關鍵性的作用。圖7所示即為經(jīng)過功耗驅(qū)動的布局布線以后的結(jié)果,時鐘走線變得更有規(guī)則,連線也盡量做到了最短,從而大大降低了功耗,通過該方式最大可以節(jié)省30%的功耗。

圖7 功耗驅(qū)動布局布線后的時鐘網(wǎng)絡

地址:廣州市天河北路689號光大銀行大廈12樓F4 電話:(020) 38730619 38731905

技術支持: (020) 28872345 22644375 E-mail:ACTEL.support@zlgmcu.com

評論