迎合三重播放業務時代需要的基礎局端 DSP(08-100)

SCR左邊的任一主單元均可直接與SCR右邊的從單元相連。主單元包括DSP的CPU、串行高速IO (SRIO)、四個傳輸控制器(TC)以及連接將三個主外設(PCI、HPI與EMAC)的連接至SCR的縱橫制端口。從單元包括DSP存儲器、DDR存儲器接口、Turbo協處理器 (TCP)、Viterbi 協處理器(VCP)以及將多個外設連接至 SCR 的縱橫制端口。

本文引用地址:http://www.104case.com/article/91839.htm這種架構既快速又高效,因為 SCR 使主從單元之間實現了真正的同時數據傳輸。例如,PCI 至 DDR EMIF 的連接獨立于 PCI 166 至 DSP CPU 的連接。數據完全是并行傳輸。當多個主單元訪問同一個從單元時,SCR 執行判優。同時系統設計人員可以通過對主單元的優先級別進行編程來施加某些控制。

架構要求

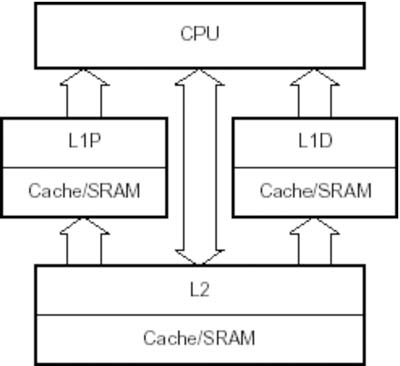

在執行算法時,CPU 與存儲器之間的指令和數據傳輸至關重要。在如圖 2 所示的 TMS320C6455 DSP 存儲器系統中,可通過使用 256 位寬的數據總線并在 CPU 與存儲器之間的內部直接存儲器存取 (DMA) 架構上創建兩層高速緩存來優化數據傳輸。

圖 2 TMS320C64x+ 內部存儲器

另一個架構要求是高效片上處理引擎。一種高效的方法是集成片上協處理器,以加速要求高性能的特定功能。例如,MS320C6455 DSP 就集成了 Viterbi 協處理器 (VCP) 與 Turbo 協處理器 (TCP),如圖 1 所示。

片上處理工作完成后,開發人員仍需將大量數據從芯片傳輸至電路板上,最終傳輸到電信傳輸介質上。顯然應選擇高速 IO,但考慮到上述的異構架構,確定哪種處理方法最佳就會變得復雜。

最佳解決方案是為片內板級接口提供多種高性能 IO 接口。SRIO 是異構多處理器器件間通信的最佳選擇,因為其高吞吐消息傳遞方案可實現 95% 的帶寬利用率(4x 串行雙向鏈路可達 10 Gb/s)。

當然,外部存儲器傳輸最好采用 32 位 DDR2 存儲器控制器;同樣,連接片外器件最好采用 66 MHz PCI 總線;處理板上或板外 IP 流量的最好選擇 1 Gb/s 以太網媒體接入控制器 (EMAC);電信專用的通用測試與操作 PHY 接口則可充分滿足 ATM (UTOPIA 2) 連接的需求。

雖然 DSP 處理能力隨著具有更強并行能力以及其它高級特性的新架構的推出而顯著提高,但電路板設計人員還可通過將多個 DSP 高效集成到單個電路板來獲取更明顯的改善。使用 SRIO 快速連接大大簡化了這項工作,因為從 DSP 軟件的角度來看,DSP 之間的數據流處理與單個 DSP 內的數據流處理并沒有很大的差異。

評論