用于CDR電路的相位插值選擇電路設計

0 引言

本文引用地址:http://www.104case.com/article/89791.htm在高速多通道串行收發系統中,由于數據在傳輸時會受到多種噪聲的影響而失真,因此在接收端要進行時鐘的恢復和數據的重定時,即時鐘數據恢復(CDR)。然而由于工藝、電壓的影響以及系統對功耗和抖動性能的要求,過去采用的各通道擁有獨立鎖相環路的方案已逐漸被設計者舍棄,取而代之的是雙環時鐘數據恢復環路。其基本思想是:時鐘數據恢復單元的各個通道共享同一個鎖相環,由該環路統一向各通道提供多相參考時鐘,各通道的CDR環路則利用已經產生的多相時鐘完成數據的重定時。這樣既避免了由于不同鎖相環輸出時鐘間的差異而造成系統性能的下降,又減小了芯片面積和系統功耗。 本文研究了時鐘數據恢復環路中多相正交參考時鐘的產生原理,根據所設計的2.5 Gbit/s CDR的要求,通過對傳統正交時鐘產生過程的分析,提出了一種新的相位插值一選擇方案,并采用0.18μmCMOS工藝實現。在SMIC 0.18μm CMOS工藝下采用Spectre進行了驗證,結果顯示該電路有效地提高了輸入抖動容限。

1 電路結構及產生方案

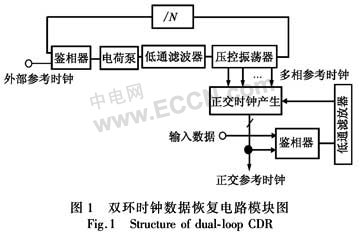

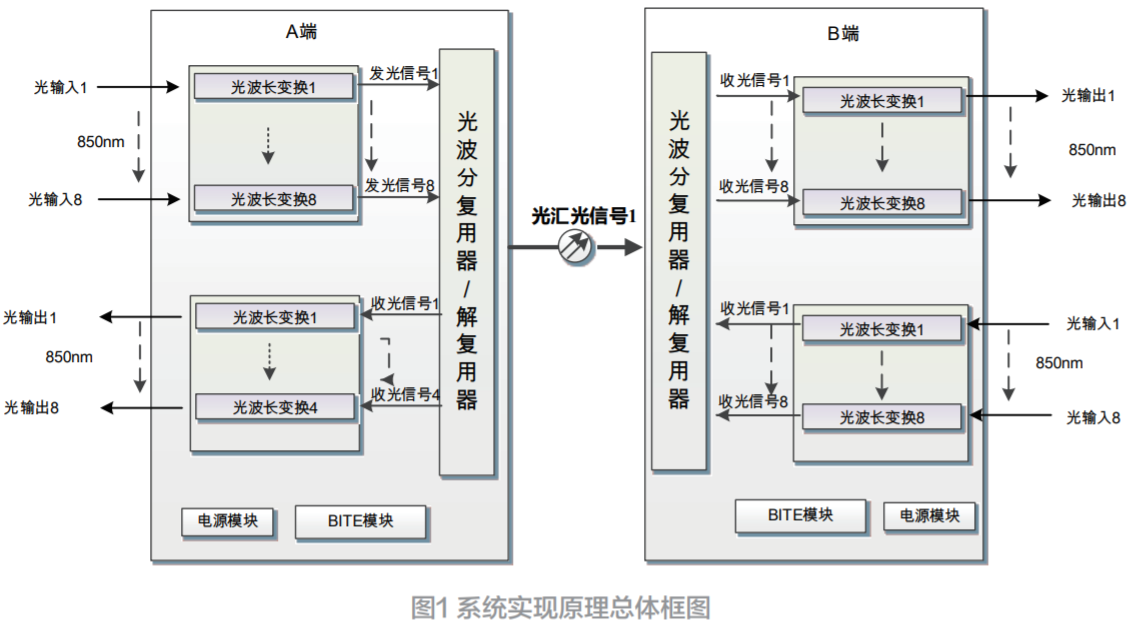

圖1給出了雙環時鐘數據恢復環路的基本結構,其中,鑒相器(PD)比較輸入數據和參考時鐘的相位,必須在且只需在數據跳變處檢測出兩者問的相位誤差,即為了進行數據的自動重定時,鑒相器必須利用時鐘對數據進行采樣,這就需要多點采樣方案。為了滿足采樣要求,參考時鐘相位的最小數目是2,文獻[1]認為數目為4是因為每個時鐘信號在差分完成方式下都自動產生了各自的互補信號,所以這里將參考時鐘相位的最小數目定為2。這兩個時鐘的相位相鄰,且呈正交關系,盡管可以采用更多的時鐘相位來降低噪聲靈敏度,但正交時鐘產生相對簡便,而且對于數據的抖動性能要求低,同時也可以降低時鐘分布網絡的復雜度以及功耗和面積。

1.1 傳統的正交時鐘產生方案

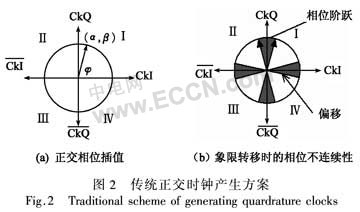

為了實現正交相位時鐘,把整個360°的插值范圍離散地劃分為4個象限,如圖2(a)所示,每個象限的插值范圍是90°。當插值向量從一個象限轉移到另一個象限時,時鐘就被它的互補時鐘所代替。為了降低抖動和相位不連續性,這種替換必須在不影響環路正常工作的情況下完成,于是采用象限邊界控制單元來保證時鐘的替換只發生在時鐘混頻權重為0的時候,這樣在理論上實現了時鐘相位所在象限的平滑轉移。然而在實際實現時,由于各種負面因素,比如相位邊界控制單元的偏移,工藝、電壓、溫度的變化等,會產生如圖2(b)所示的相位階躍,從而導致抖動性能的下降,時鐘的偏移較大。

1.2相位插值-相位選擇的正交時鐘產生方案

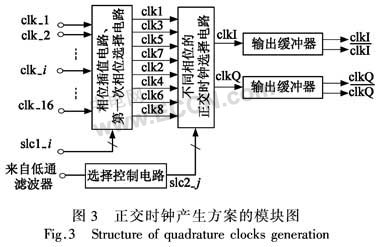

相位插值一相位選擇的正交時鐘產生方案可描述為:首先由圖1所示的第一個環路產生16相標準參考時鐘,相位間隔為2π/16,即π/8,每個時鐘clk_i的相位可以表示為Pclk_i=(i-1)π/8;然后利用每兩個相鄰相位的時鐘進行插值,從而得到32相參考時鐘,此時得到的插值后時鐘與其相鄰時鐘相位間隔為π/16,時鐘clk_i和clk_i+1進行插值后得到的時鐘相位可以表示為Pclk_i,i+1=iπ/8-π/16;在進行時鐘相位插值的同時對32相時鐘進行第一次相位選擇,選擇出8相兩組時鐘clk1~clk8,其中clk1、3、5、7組和clk2、4、6、8組的組內相鄰相位問隔為π/2,而且每組內部4個時鐘各有4個不同相位,相位問隔為π/16;之后根據低通濾波器對鑒相器工作結果的譯碼,得出在這兩組正交時鐘中的選擇方案,即相位的選擇,最后把選擇后的時鐘送人輸出緩沖器,完成單端到雙端的轉換,生成各時鐘的互補時鐘送到后續的半速率鑒相器中完成數據的重定時工作。

這樣就完成了正交時鐘的生成工作,該對正交時鐘在完成數據重定時的過程中,相位的調整步伐為π/16,即數據周期的1/32,可以達到數據重定時的精度要求。圖3所示為正交時鐘產生方案的模塊圖。

2 實現電路及晶體管級仿真

2.1 相位插值及第一次相位選擇電路

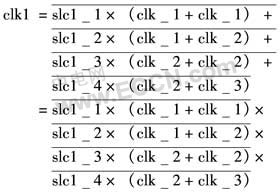

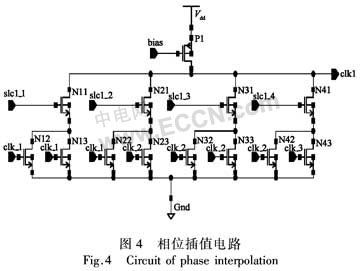

根據上文,從圖1所示的第一個環路送出的16相參考時鐘進入正交時鐘產生模塊后,首先完成相位的插值操作,生成32相參考時鐘。這里把16相參考時鐘信號進行相鄰交叉重疊分組,共分8組,分別送人8個相位插值電路。每個相位插值電路對輸入時鐘完成插值操作后,經slc_i,i=1、2、3、4信號選擇出一相,共得到8個相位的時鐘。圖4所示為一組相位插值電路圖,從圖中可以看出該組相位插值電路的輸出時鐘信號clk1的表達式為(其余7組類似)

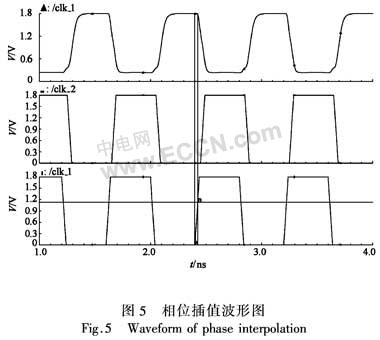

四個選擇信號slcl_1、slcl_2、slcl_3、slcl_4同一時間內只有一個有效,比如slcl_2信號為高時,輸出為clk_1與clk_2進行相位插值后的結果。設計中N12、N13、N22、N23、N32、N33、N42、N43具有相同的寬長比,N11、N21、N31、N41有相同的寬長比且其寬長比為N12寬長比的兩倍。以slcl_2信號有效為例,輸出節點clkl的上升時間由P1決定;下降時間與對clkl節點負載電容的放電電流成正比,僅由N22和N23的導通情況決定,N22和N23同時導通時其放電電流是N22和N23僅有一個導通時的兩倍,將N22和N23同時導通時clkl的下降時間記為τ,則N22和N23僅有一個導通時clkl的下降時間為2τ。如果N23輸入上升沿滯后于N22輸入上升沿的時間小于τ,從N22輸入上升沿時刻到N23輸入上升沿這段時間內的放電電流是N23輸入上升沿之后放電電流的1/2。記N23輸入上升沿滯后于N22輸入上升沿的時間為T,這種情況下總的延時約為T+(2τ-T)/2=τ+T/2;輸出信號的相位位于clk_1和clk_2相位差的1/2處,實現了相位插值。其插值過程波形可用Cadence Spectre仿真得到,如圖5所示。

這里注意到有些進行插值的時鐘是同一個時鐘信號,這是為了使各種情況下輸出時鐘信號的延時相匹配。

這個相位插值電路只要滿足T<τ就可以在很寬的時鐘范圍之內實現相位插值,所產生的時鐘相位與電源電壓、工作溫度無關,僅取決于用于插值的NMOS管尺寸的匹配程度,通過版圖設計可以將用于插值的NMOS管的不匹配程度降到最低。輸出相位的穩定程度只取決于輸入時鐘的穩定程度,不會降低電路的抖動指標。

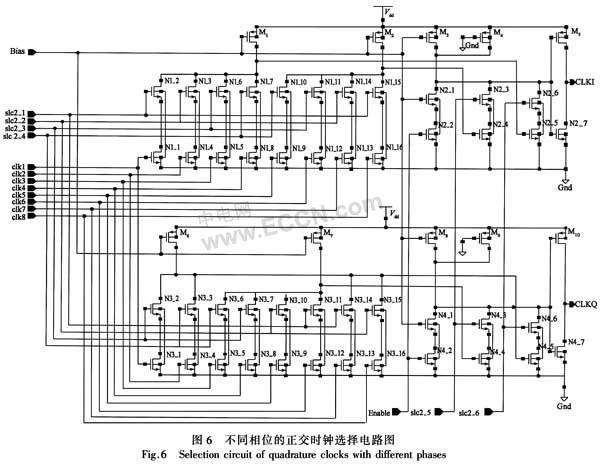

2.2不同相位的正交時鐘選擇電路

經過第一次時鐘相位的選擇,已經得到了相位正交的參考時鐘,但是還需要選擇用哪一對正交時鐘對輸入的數據進行重定時。圖6所示為正交時鐘的選擇電路圖,最終選擇輸出的時鐘信號clkI和clkQ對應的時鐘彼此正交,其相位關系與行為描述一致:slc2_5信號有效時,clkI的相位在π和2π之間,按照slc2_1、slc2_2、slc2_3、slcl_4的順序依次有效,輸出時鐘clkI的相位遞減,步長為π/4;slc2_6信號有效時,clkI的相位在0和π之間,按照slc2_1、slc2_2、slc2_3、slcl_4的順序依次有效,輸出時鐘clkI的相位遞增,步長為π/4。

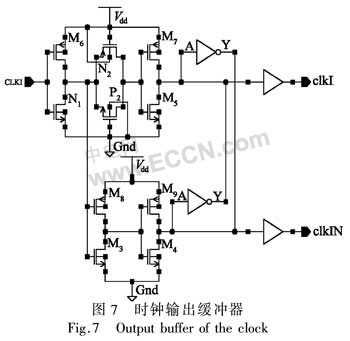

2.3時鐘輸出緩沖器

為了增加電路的驅動能力,并產生兩個正交時鐘的互補信號用于后續的半速率鑒相器等電路,在把時鐘信號clkI和clkQ送人后續電路進行數據恢復之前,先將其送入如圖7所示的時鐘緩沖器。時鐘信號在此經過緩沖放大,而且兩個互補時鐘信號的輸出彼此構成正反饋,提高了轉換速率。

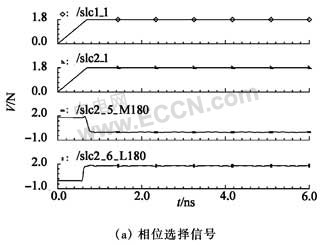

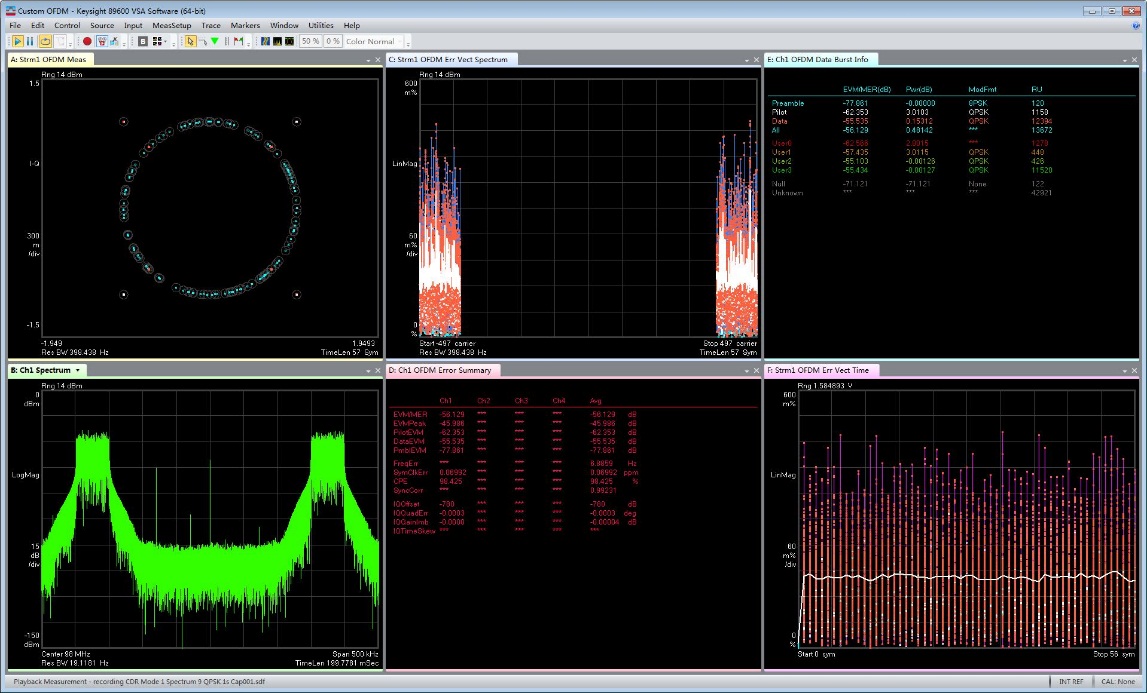

2.4 總體電路的晶體管級仿真

采用Cadence Spectre在0.18μm CMOS工藝庫下對整個電路進行晶體管級仿真,結果如圖8所示。電路的輸入是16相頻率為1.25 GHz,即周期為800 ps、相鄰相差為π/8,即相差50 ps的時鐘,以及相位選擇信號,從圖8可以看到插值后的時鐘與預期一致,所分兩組時鐘組內相差為200.47 ps和201.472 ps,呈正交關系。

3 結論

本文描述了雙環時鐘數據恢復電路利用相位正交的參考時鐘進行工作的原理,通過對傳統的正交時鐘產生過程的分析和現有電路的改進,提出了一種相位插值一相位選擇產生方案,并進行了理論分析,同時在TSMC 0.18μm CMOS仿真工藝Spectre環境下進行了驗證。該電路與電源電壓、工作溫度和工藝無關,在輸出的相位上不會引入附加抖動,在數據時鐘恢復電路中應用相比采用傳統電路可以提高輸入抖動容限。

低通濾波器相關文章:低通濾波器原理

電流傳感器相關文章:電流傳感器原理 鑒相器相關文章:鑒相器原理 鎖相環相關文章:鎖相環原理

評論