FPGA的多路可控脈沖延遲系統(tǒng)

摘要 采用數(shù)字方法和模擬方法設(shè)計了一種最大分辨率為0.15 ns級的多路脈沖延遲系統(tǒng),可以實現(xiàn)對連續(xù)脈沖信號的高分辨率可控延遲;采用Flash FPGA克服了現(xiàn)有SRAM FPGA系統(tǒng)掉電后程序丟失的缺點,提高了系統(tǒng)反應(yīng)速度。本系統(tǒng)適用于需要將輸入脈沖信號進(jìn)行精確延遲來產(chǎn)生測試或控制用的連續(xù)脈沖信號場合,具有很強(qiáng)的適用性。

本文引用地址:http://www.104case.com/article/88050.htm關(guān)鍵詞 數(shù)字方法 模擬方法 分辨率 脈沖延遲 ProASIC3

在科學(xué)研究、通信和一些自動控制中,經(jīng)常需要精確定時的連續(xù)脈沖信號,用于產(chǎn)生測試信號或控制用的時序。脈沖延遲的基本方法可分為數(shù)字方法和模擬方法。數(shù)字方法采用計數(shù)器或存儲器實現(xiàn)延遲控制,其缺點是無法滿足高分辨率的要求;模擬方法采用專用的脈沖延遲器件實現(xiàn)延遲控制,其缺點是抗干擾效果不好,容易產(chǎn)生抖動和電壓不穩(wěn)等問題。于是我們提出構(gòu)建數(shù)模結(jié)合的系統(tǒng),實現(xiàn)連續(xù)脈沖信號的高分辨率延遲。

1 系統(tǒng)功能

本系統(tǒng)擬定對頻率范圍在1~50 kHz左右的TTL電平脈沖序列進(jìn)行多路延遲處理。各路延遲時間分別由單片機(jī)動態(tài)設(shè)定,最大延遲時間為1 ms,最大分辨率為0.15 ns級。

2 方案選擇

因為所要處理的脈沖序列的脈沖間隔時間大于脈沖延遲時間,不必考慮多脈沖存儲和再生的問題,所以數(shù)字方法中選用計數(shù)器法,完成延遲量高位部分控制。現(xiàn)存的計數(shù)器系統(tǒng)方案大多是基于SRAM的FPGA,其缺點是SRAM中的程序掉電后易丟失,上電后要借助于外圍的單片機(jī)重新向SRAM中寫程序,影響了系統(tǒng)的反應(yīng)速度。為了解決這一問題,系統(tǒng)選用Actel公司的Flash FPGA,掉電后程序不易丟失,提高了系統(tǒng)的反應(yīng)速度。另外,F(xiàn)PGA中的PLL模塊能對外部時鐘源進(jìn)行分頻、倍頻,給計數(shù)器模塊提供觸發(fā)和計數(shù)脈沖。這些大大減少了芯片數(shù)目,提高了集成度,節(jié)省了系統(tǒng)面積和成本。然后,用VHDL語言對FPGA進(jìn)行編程,實現(xiàn)硬件電路軟件化設(shè)計,控制各路時序,完成用數(shù)字方法對脈沖信號的延遲控制,此時分辨率可以達(dá)到10 ns級。

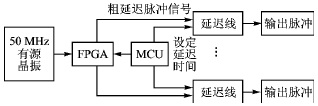

用模擬方法進(jìn)行延遲低位部分控制時,選用了DS1020延遲線芯片。只要在電路板上搭建多組以DS1020延遲線芯片為主的電路,就可以同時輸出多路脈沖序列。此時最大延遲分辨率可以達(dá)到0.15 ns級。本方案中各路計數(shù)器模塊和延遲線的延遲時間均可由MCU編程來動態(tài)調(diào)整,系統(tǒng)結(jié)構(gòu)框圖如圖1所示。

圖1 系統(tǒng)結(jié)構(gòu)框圖

3 方案實現(xiàn)

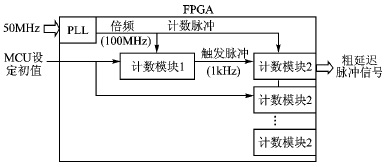

系統(tǒng)選用Actel公司的ProASIC3 A3P250芯片實現(xiàn)數(shù)字部分。系統(tǒng)時鐘由外部50 MHz晶振提供,時鐘引腳連接到FPGA的CCC全局時鐘引腳上;頻率可以通過FPGA內(nèi)部的PLL實現(xiàn)倍頻和分頻,設(shè)定需要的頻率。因為在多路脈沖延遲方案中電路的同步是保證控制準(zhǔn)確的前提,所以應(yīng)該首先為電路提供一個基準(zhǔn)脈沖。通過PLL將50 MHz的頻率倍頻,產(chǎn)生一個100 MHz的低頻觸發(fā)脈沖,從而觸發(fā)各路計數(shù)模塊開始計數(shù)。同時,將100 MHz通過另一計數(shù)器模塊得到1 kHz的觸發(fā)脈沖,此時可以根據(jù)需要延遲的范圍通過MCU編程來設(shè)定各計數(shù)器的初值,產(chǎn)生一個粗延遲的脈沖信號,實現(xiàn)以10 ns為步進(jìn)的延遲,延遲分辨率為10 ns級。FPGA內(nèi)部結(jié)構(gòu)如圖2所示。

圖2 FPGA內(nèi)部結(jié)構(gòu)框圖

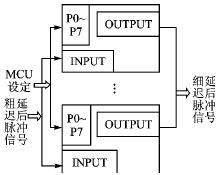

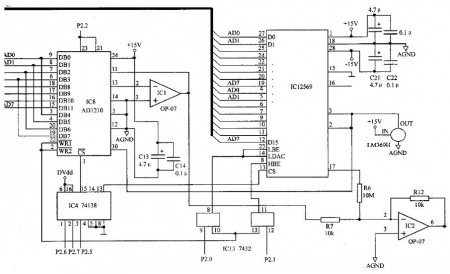

FPGA將粗延遲脈沖信號送給多路延遲線芯片DS1020進(jìn)行低位延遲。實際電路中DS1020的8個并行數(shù)據(jù)引腳(P0~P7)與MCU相連,MCU通過軟件程序?qū)⒀舆t時間寫入DS1020,并發(fā)送指令給EN端口,通知DS1020實現(xiàn)低位延時。通過與MCU相連的8位數(shù)據(jù)腳實現(xiàn)10 ns以內(nèi)的延時,最后輸出腳OUTPUT將脈沖信號送至D/A轉(zhuǎn)換器,再經(jīng)放大器放大后得到總延遲后的輸出信號。多路延遲線結(jié)構(gòu)框圖如圖3所示。

圖3 多路延遲線結(jié)構(gòu)框圖

4 系統(tǒng)仿真

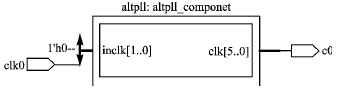

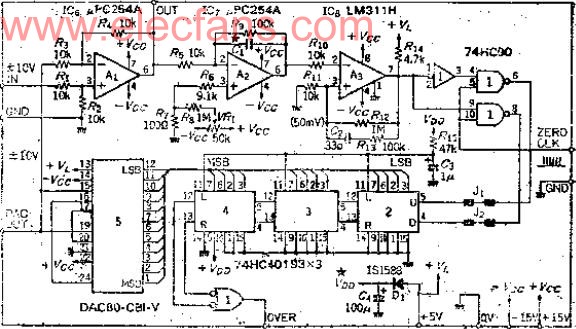

下面給出了核心部分的RTL圖及QuartusII時序仿真波形。PLL模塊的RTL圖如圖4所示。

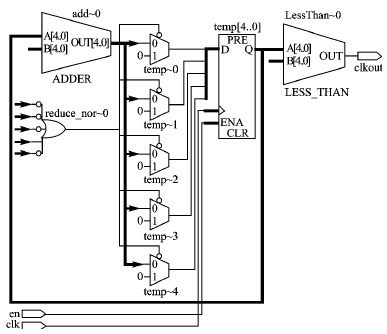

計數(shù)模塊2的RTL圖如圖5所示。該模塊的輸入clk應(yīng)連接到頻率為100 MHz的時鐘信號,作為計數(shù)脈沖。 en是使能信號,應(yīng)連接到經(jīng)過計數(shù)模塊1分頻后得到的1 kHz的時鐘信號上。假設(shè)en信號到來,該信號為高電平時,計數(shù)器temp開始計數(shù),到達(dá)設(shè)定的計數(shù)時間后輸出高電平,否則為低電平。經(jīng)過計數(shù)模塊2后系統(tǒng)完成粗延遲,此時延遲分辨率為10 ns級。

圖4 PLL模塊RTL圖

圖5 計數(shù)模塊2的RTL圖

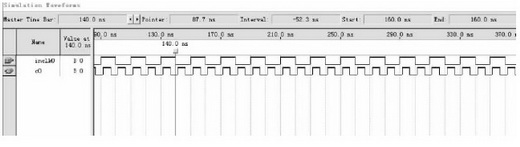

PLL模塊實現(xiàn)倍頻的功能。其中,輸入clk0應(yīng)連接頻率為50 MHz的時鐘信號。輸出信號c0為100 MHz,分別送給計數(shù)模塊1和2實現(xiàn)分頻和計數(shù)脈沖的作用。其仿真波形如圖6所示。

圖6 PLL模塊仿真波形

計數(shù)模塊1和2的延遲時間均可由單片機(jī)動態(tài)寫入,本方針波形寫入的延遲時間為300 ns。延遲后的波形如圖7所示。

結(jié)語

本設(shè)計不同于現(xiàn)有的延遲電路,它將數(shù)字方法圖7延遲后計數(shù)模塊2輸出波形和模擬方法相結(jié)合,對多路連續(xù)脈沖信號進(jìn)行大范圍高分辨率的動態(tài)延遲,將分辨率提高到了0.15 ns級。而且,本系統(tǒng)用Flash FPGA替代現(xiàn)有系統(tǒng)的SRAM FPGA,從而大大提高了系統(tǒng)集成度,降低了成本。

參考文獻(xiàn)

[1] 侯伯亨,顧新.VHDL硬件描述語言與數(shù)字邏輯電路設(shè)計[M].西安:西安電子科技大學(xué)出版社,1999.

[2] 劉豫晉,廖佳,楚然.連續(xù)脈沖信號延遲線的實現(xiàn)[J].計算機(jī)應(yīng)用,2002,28(9).

[3] 高輝,陳文通,王金祥,等.可編程器件在納秒級多通道數(shù)字延遲/脈沖發(fā)生器中的應(yīng)用[J].分析儀器,2002(3).

[4] 王道憲.CPLD/FPGA可編程邏輯器件應(yīng)用與開發(fā)[M]. 北京: 國防工業(yè)出版社, 2004.

[5] Analog Device Inc. Digitally Programmable Delay Generator AD9501,2003.

程璐(碩士研究生)、郭文成(副教授),主要研究方向為微機(jī)控制系統(tǒng)。

評論