FFT實時譜分析系統的FPGA設計和實現

在一個基-4蝶形運算單元中,包含WP、W2P和W3P三個旋轉因子,每組基-4蝶形運算的第一個輸出數據所乘的旋轉因子總為1。在同一個蝶形組內,p值是不變的,因而只需確定一個p值,三個旋轉因子便可確定下來。每當一個基-4蝶形組計算完畢而轉入下一個蝶形組時,p值改變一次,其變化的順序恰好是(L-1)位四進制數順序加1的倒序輸出。由此可以根據蝶形運算的級數和四點FFT的節點位置計算出對應的旋轉因子的角度。

由于

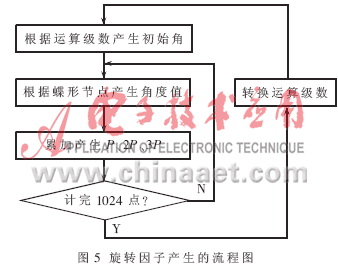

本設計的復乘運算采用CORDIC算法實現,需要輸入角度值作為進行復乘運算的相應旋轉因子的角度,因此旋轉因子產生模塊輸出的數據即對應旋轉因子的角度值,模塊中包括10位計數器和一個計算輸出進程。程序的運算流程如圖5所示。

本設計采用直接計算旋轉因子的方法,不需要產生旋轉因子的讀取地址和額外的ROM資源,簡化了設計,但需要一直進行角度值的計算,增加了系統的運算時間。

3 FFT實時頻譜分析系統的實現

本設計采用Synplicity公司的邏輯綜合軟件Synplify7.1 pro進行設計綜合,用Xilinx的ISE6.1布局布線。實現后的系統的時序分析結果表示,系統有9.139ns的延遲,系統時鐘周期可達10.817ns,系統頻率達到92.4MHz。當系統頻率為90MHz時,1024點FFT運算需要的時間大約為68.3μs,完全可以滿足實時處理的要求。本文采用Xilinx公司的Virtex-Ⅱxc2v500 fg456-5 FPGA器件實現系統,設計使用資源狀況如表1所示。

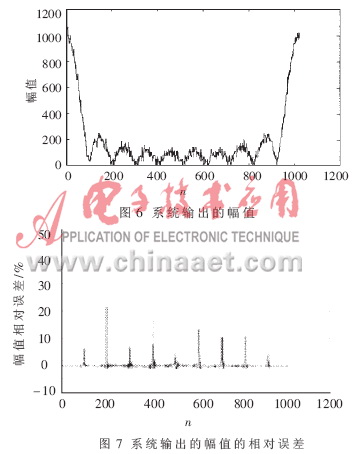

本FFT實時譜分析系統采用定點運算方案,輸入為12位復數數據,輸出為14位復數數據。采用方波信號進行測試,其參數為:脈沖幅度H=100,脈沖寬度M=10。本FFT實時譜分析系統輸出的幅值如圖6所示,輸出的幅值的相對誤差如圖7所示。相對誤差較大的一些點均出現在標準FFT輸出的幅值很小的點上,這是由于有限字長效應引起相對誤差造成的。同時由于采用的算術運算方案是定點運算,加劇了小信號的信噪比的惡化。但在實際應用中這些輸出幅值很小的點會被判別為頻譜上的噪聲點,對實際的頻譜分析影響不大,故對系統的誤差影響并不大。而在標準FFT輸出的幅值較大的點上,相對誤差則很小。

本設計全部由VHDL語言實現,采用自頂向下的設計方法,完成了一個1024點FFT實時譜分析系統。該FFT采用了基-4原位算法,既保證了運算速度,又節省了硬件資源。該FFT通過CORDIC算法實現復乘,較傳統的復乘運算節省了大量的ROM資源,同時采用了流水線結構,加快了運算速度。

參考文獻

1 劉淩,胡永生. 數字信號處理的FPGA實現. 北京:清華大學出版社,2002

2 李廣軍,孟憲元. 可編程ASIC 設計及應用[M].成都:電子科技大學出版社,2000

3 劉朝暉, 韓月秋.用FPGA 實現FFT 的研究[J].北京:北京理工大學學報,1999;19(2):234~238

4 Volder J E.The CORDIC Trigonometric Computing Technique IRE.Trans.on Electronic Computer,1959(9)

評論