FFT實(shí)時(shí)譜分析系統(tǒng)的FPGA設(shè)計(jì)和實(shí)現(xiàn)

摘要: 采用按時(shí)間抽選的基4原位算法和坐標(biāo)旋轉(zhuǎn)數(shù)字式計(jì)算機(jī)(CORDIC)算法實(shí)現(xiàn)了一個(gè)FFT實(shí)時(shí)譜分析系統(tǒng)。整個(gè)設(shè)計(jì)采用流水線工作方式,保證了系統(tǒng)的速度,避免了瓶頸的出現(xiàn);整個(gè)系統(tǒng)采用FPGA實(shí)現(xiàn),實(shí)驗(yàn)表明,該系統(tǒng)既有DSP器件實(shí)現(xiàn)的靈活性又有專用 FFT芯片實(shí)現(xiàn)的高速數(shù)據(jù)吞吐能力,可以廣泛地應(yīng)用于數(shù)字信號(hào)處理的各個(gè)領(lǐng)域。

關(guān)鍵詞: 快速傅里葉變換 CORDIC算法 現(xiàn)場(chǎng)可編程門陣列(FPGA)

快速傅里葉變換(Fast Fourier Transformation, FFT) 實(shí)時(shí)譜分析是DSP應(yīng)用的核心技術(shù)之一,而在高速實(shí)時(shí)信號(hào)處理中,常采用專門集成電路(ASIC)來(lái)實(shí)現(xiàn)。FPGA是一種具有大量的可編程邏輯單元的器件,它的應(yīng)用使得電子產(chǎn)品不僅具有高速度、高集成度和高可靠性,而且具有用戶可編程特性,能降低設(shè)計(jì)風(fēng)險(xiǎn)。實(shí)驗(yàn)表明,用FPGA實(shí)現(xiàn)的實(shí)時(shí)譜分析系統(tǒng)既有專用ASIC電路實(shí)現(xiàn)的快速性,又有DSP器件實(shí)現(xiàn)的靈活性,非常適用于高速實(shí)時(shí)的數(shù)字信號(hào)處理。

1 FFT實(shí)時(shí)信號(hào)處理系統(tǒng)的總體設(shè)計(jì)

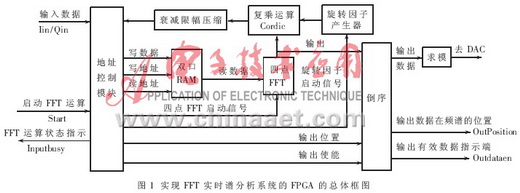

FFT頻譜分析系統(tǒng)主要由1024點(diǎn)基-4 FFT模塊和接口控制電路組成。其中,基-4 FFT模塊用于實(shí)現(xiàn)一組1024點(diǎn)復(fù)數(shù)數(shù)據(jù)的FFT變換;接口控制電路負(fù)責(zé)控制1024點(diǎn)基-4 FFT模塊,并對(duì)A/D采樣輸出的數(shù)據(jù)進(jìn)行緩存、速率匹配等,協(xié)調(diào)整個(gè)FFT頻譜分析系統(tǒng)的工作時(shí)序。

在本設(shè)計(jì)中,F(xiàn)FT實(shí)時(shí)譜分析系統(tǒng)的1024點(diǎn)基-4 FFT算法采用FPGA實(shí)現(xiàn)。FPGA的總體框圖如圖1所示。其中,衰減限幅模塊負(fù)責(zé)對(duì)數(shù)據(jù)進(jìn)行衰減及限幅壓縮處理;雙口RAM負(fù)責(zé)存儲(chǔ)外部輸入的原始數(shù)據(jù)及經(jīng)過(guò)蝶形運(yùn)算后的中間數(shù)據(jù);四點(diǎn)FFT模塊完成4點(diǎn)DFT運(yùn)算;地址控制模塊負(fù)責(zé)產(chǎn)生讀地址、寫地址、寫使能信號(hào)以及相關(guān)模塊的啟動(dòng)、控制信號(hào),是FFT系統(tǒng)的控制核心;復(fù)乘運(yùn)算模塊是系統(tǒng)運(yùn)算的核心部分,采用CORDIC算法實(shí)現(xiàn);旋轉(zhuǎn)因子產(chǎn)生器產(chǎn)生復(fù)乘運(yùn)算中的旋轉(zhuǎn)因子的角度數(shù)據(jù);倒序模塊實(shí)現(xiàn)頻譜正常順序輸出。

2 功能模塊的設(shè)計(jì)

2.1 衰減限幅模塊

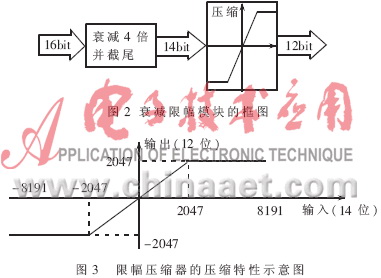

FFT實(shí)時(shí)譜分析系統(tǒng)采用的算術(shù)運(yùn)算方案是定點(diǎn)運(yùn)算,衰減限幅模塊實(shí)現(xiàn)了定比例衰減、尾數(shù)處理和壓縮信號(hào)電平的作用,用以防止數(shù)據(jù)溢出。模塊框圖如圖2所示,其壓縮特性如圖3所示。

2.2 四點(diǎn)FFT模塊

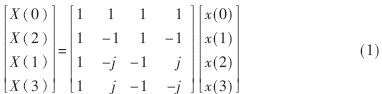

四點(diǎn)FFT模塊完成四點(diǎn)DFT變換,變換公式如下:

四點(diǎn)FFT模塊中完全不需要復(fù)數(shù)乘法,乘-j只需將實(shí)部虛部交換,再加上必要的正負(fù)號(hào)即可。四點(diǎn)FFT模塊采用流水線工作方式,每四個(gè)時(shí)鐘周期完成一組四點(diǎn)FFT運(yùn)算。在輸入一組四點(diǎn)原始數(shù)據(jù)x(i)時(shí),要完成兩項(xiàng)工作:①進(jìn)行上一組四點(diǎn)FFT的第二級(jí)運(yùn)算,即計(jì)算并輸出上一組四點(diǎn)FFT的結(jié)果X(k);②進(jìn)行本組四點(diǎn)FFT的第一級(jí)運(yùn)算,即計(jì)算本組四點(diǎn)FFT的中間結(jié)果X′(k)。這樣充分利用了硬件資源。

2.3 復(fù)乘運(yùn)算模塊

復(fù)乘運(yùn)算是FFT處理器中兩種最頻繁的運(yùn)算之一,因而復(fù)乘運(yùn)算模塊也是FFT處理器中的一個(gè)重要模塊。輸入復(fù)數(shù)數(shù)據(jù)xr+jxi與旋轉(zhuǎn)因子cosα+jsinα相乘的公式為:

![]()

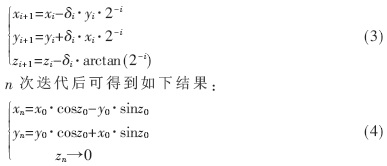

利用CORDIC的圓周旋轉(zhuǎn)的向量工作模式可以實(shí)現(xiàn)復(fù)乘運(yùn)算,所采用的迭代方程組如下:

所以,只需將需要運(yùn)算的角度值作為z0輸入,經(jīng)過(guò)旋轉(zhuǎn)迭代后,迭代結(jié)果的xn和yn就是所需要的旋轉(zhuǎn)因子![]() 復(fù)乘的運(yùn)算值。即:

復(fù)乘的運(yùn)算值。即:

![]()

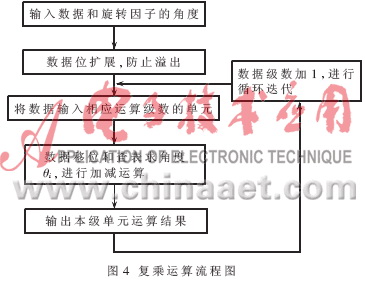

復(fù)乘運(yùn)算模塊的工作流程如圖4所示。

從復(fù)乘運(yùn)算的算法流程中可以看到,實(shí)現(xiàn)復(fù)乘運(yùn)算的主要元件有加法器、移位器和多選一數(shù)據(jù)選擇器等。組成流水線后,各流水單元結(jié)構(gòu)相似,很適合用FPGA實(shí)現(xiàn)。

評(píng)論