可定制軟微處理器內核的配置策略

可定制微處理器內核有兩個特性:可配置性和可擴展性。可配置性是指設計工程師可以更改處理器的現有特性。可擴展性是指能加入處理器本身沒有的功能特點,從而增加處理器的基本功能。

本文引用地址:http://www.104case.com/article/85720.htm從底層修改CPU結構的能力使得用戶可定制處理器很顯著地區別于傳統的結構固定的CPU,設計工程師在設計處理器功能時有更大的自由度,例如:在設計時可以根據具體的應用需要定義一組指令;加入新的通用寄存器;定義新的條件代碼;根據在仿真器上運行的軟件反饋信息來精細地調整指令和數據緩存的大小和結構;在SRAM或邏輯電路內實現內核寄存器文件以及加入本地中間結果暫存RAM;加入強大的DSP處理功能,如乘法累加(MAC)指令和本地XY數據存儲器。

此外,輸入輸出(I/O)的配置也很靈活。為了達到高的I/O速率,設計工程師可以將指令總線和數據總線分開(哈佛結構);為了減少管腳數和減小封裝成本,數據和指令總線用統一總線(馮•諾曼結構)。可以把特定應用邏輯與處理器內核緊密相連,用其本身的I/O總線加入輔助寄存器文件。用戶定義的指令可以提高一些關鍵軟件算法的性能,從而提高整個系統的性能。

以前這種設計只能是由CPU廠商的高級工程師完成。在可綜合的HDL、先進的EDA工具以及可定制的軟處理器內核出現后,一般的嵌入式系統設計工程師在他們的SoC、ASIC和ASSP設計時就擁有控制系統架構的自由。

可定制IP的優越性

采用IP供應商提供的微處理器可綜合HDL源代碼(VHDL或Verilog格式)的優點包括:軟內核獨立于加工工藝、庫、代工廠,因此在生產上有很大的靈活性;用戶可以在這些HDL源代碼基礎上進行修改并保護專有的技術訣竅。

對用戶可定制處理器內核進行開發的初期,只有IP供應商定義的最低限度的規范或基本內核。對于一些不需特別優化的深度嵌入式應用可以使用這種基本內核。但是,可定制處理器的真正魅力是其可被修改的特點,設計工程師可以對基本內核進行配置并根據需要進行功能擴展。

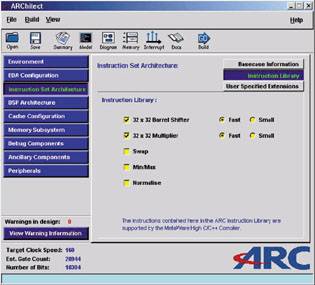

對可定制處理器的配置和功能擴展并不一定采用HDL編碼。通過處理器配置圖形工具,設計工程師甚至不用看HDL源代碼就可以作大量的修改。通過簡單的“點擊、選擇”界面進行選項設置,配置工具能自動生成HDL文件以及用于邏輯綜合的腳本文件。例如對于ARCtangen-A4處理器, ARC處理器內核提供如圖所示的ARChitect配置工具。

ARChitect工具允許設計工程師設置和擴展指令集、中斷、指令緩存、數據緩存、存儲器子系統以及DSP功能,還可以加入外圍器件,如以太網的媒體訪問控制器(MAC)以及用于實時處理的32位計時器。另外一個可選的設置是時鐘選通,可以關斷部分不需要的電路,具有節電功能。

ARCtangen-A4處理器的基本指令集包括所有的基本算術指令、邏輯指令、加載/存儲以及分支/跳轉操作指令,這些指令是典型的嵌入式應用所必需的。通過使用ARChitect工具,設計工程師可以從一個庫中選擇另外的指令和功能特點。例如,一個硬件可控陣列移位器(hardware barrel shifter)和相關的指令尤其適合用于網絡信息處理中在數據包中插入或提取數據包頭或一段數據位。還有兩個不同的硬件乘法器可以用來加速算術功能以及其它任務的處理。用于數字信號應用的DSP指令還能在內核中優化。

可定制處理器供應商不可能預料到系統設計工程師需求的所有擴展指令,因為用戶定義的指令需要進行HDL編碼。為精簡這種擴展處理過程,處理器HDL源代碼的設計中已經考慮了這種擴展,在原代碼內已經清楚地對用戶插入代碼進行了標記和文件接口。

另外,所加入的額外寄存器非常有用,在配合用戶指令和其它邏輯功能時尤其如此。例如,一個“智能”寄存器能自動地對寫入該寄存器的值進行四舍五入處理;輔助寄存器與用戶邏輯和外圍器件一起能實現高性能的I/O。

用戶條件代碼是另外一個使軟件更智能化的方法。在ARCtangen-A4處理器條件下,條件指令集允許通過讀一個條件代碼(狀態標志)來決定每個指令是否執行。設計工程師可以為實現某個目標來建立自己的條件代碼。例如,網絡處理器在從網絡收到一個數據包時可能會設置一個標志位。基本指令和用戶定義指令可以根據條件代碼的狀態有條件地執行。

在整個開發周期中,設計工程師可以在可定制處理器中反復分配硬件和軟件的任務。例如,可以通過仿真器和設計工具中Profiler提供的反饋信息,讓那些性能很關鍵的軟件由用戶指令來實現。可以定義專用操作數、助記符、寄存器和功能,從而使設計工程師能把內部循環操作由硬件來實現,進而執行復雜多周期指令,提高處理器的速度性能。這不僅提高了性能,而且使產品的硬件多樣化,通過提高盜版難度達到保護知識產權的目的。

定制功能并不意味著總要進行功能擴展。設計工程師也可以從處理器中去除不需要的指令和其它功能,減小處理器的門數,降低功耗和制造成本。

靈活的緩存結構

在配置可定制處理器內核時,設計工程師需要注意緩存結構對功耗和硅片面積的影響。因此要均衡考慮指令緩存和數據緩存的結構。

從廣義上說,緩存結構包括直接映射(direct mapped)和多路(multiway)配置兩類。這兩種結構都互有優缺點,要根據具體的應用來選擇最佳的類型。

直接映射緩存是兩者中較簡單的一類,因此需要的門數較少。功耗是門數的函數,所以直接映射緩存的功耗小。但如果直接映射產生的緩存空間丟失(miss)比多路配置緩存更多,那么由于處理器需要經常訪問存儲器,功耗反而會增加。

實際上功耗并不是唯一的考慮因素,在有些應用中不允許太多的緩存丟失。例如,由于音頻處理是一個實時處理過程,頻繁的緩存丟失會造成音頻質量下降。多路緩存能改善直接映射緩存的不確定性,提高有效訪問率,但其代價是功耗更大和門數更多。設計工程師在做選擇時常常難以權衡。例如,在設計電池供電的MP3音播放器時,一方面多路緩存適合于實時的音頻處理,另一方面多路緩存功耗更大。這個矛盾可以從優化緩存的大小和結構來解決。利用現在先進的仿真工具對設計會有很大的幫助。

好的緩存設計還有其它的要求。例如線鎖(line locking)功能,能對部分的緩存進行保護以避免在出現緩存遺失時被處理器刷新。

傳統的CPU結構是固定的,設計工程師只能對其作很少的修改甚至是不能改動。而用戶可制定的處理器卻給設計工程師帶來了最大的自由度,能根據具體的應用進行真正的最優化設計。

本文結論

如果微處理器以可定制軟IP 形式提供時,在項目進行的任何階段都可以進行修改。設計工程師可以在他們原有的設計基礎上改變,而不必放棄原來的設計從零開始,這樣更能滿足快速變化的市場要求。如果產品規范發展到使原來的軟件運行緩慢,設計工程師可以改變可定制處理器來解決這個問題。如果要降低成本,設計工程師可以從硬件和軟件中去除一些功能。可定制軟IP讓真正了解設計的工程師可以設計出滿足需要的最優化CPU。

評論