高分辨率ADC的板布線(07-100)

高速ADC(模/數(shù)變換器)是各種應(yīng)用領(lǐng)域(如質(zhì)譜儀,超聲,激光雷達(dá)/雷達(dá),電信收發(fā)機(jī)模塊等)中關(guān)鍵的模擬處理元件。無論應(yīng)用是基于時(shí)域或頻域,都需要ADC最高的動態(tài)性能。更快和更高分辨率的ADC,可使超聲系統(tǒng)具有更詳明的圖像,使通信系統(tǒng)具有更高數(shù)據(jù)的處理能力。

隨著14位或更高分辨率ADC的采樣率繼續(xù)提高到百兆采樣范圍,隨之而來的是系統(tǒng)設(shè)計(jì)人員必須成為時(shí)鐘設(shè)計(jì)和分配及板布線方面的專家。

本文描述的是系統(tǒng)設(shè)計(jì)方面的一些關(guān)鍵性問題,特別關(guān)注印制電路板(PCB)地和電源平面布線技術(shù)。現(xiàn)代化的ADC需要現(xiàn)代化的板設(shè)計(jì)。沒有精確的時(shí)鐘源或仔細(xì)設(shè)計(jì)的板布線,則高性能變換器將達(dá)不到其性能指標(biāo)。

單IF外差接收機(jī)結(jié)構(gòu)和高級的功率放大器線性化算法,正在對ADC性能提出要求。這樣的系統(tǒng)正在把變換器的固有抖動性能推向低于1/2 PS。同樣,測試儀器工程師需要在寬帶內(nèi)有非常低的噪聲性能,以便高級頻譜分析儀開發(fā)。

因此,高速數(shù)據(jù)變換系統(tǒng)中最重要的子電路是時(shí)鐘源。這是因?yàn)闀r(shí)鐘信號的定時(shí)精度會直接影響ADC的動態(tài)性能。

為了使這種影響最小,ADC時(shí)鐘源必須具有非常低的定時(shí)抖動或相位噪聲。若在選擇時(shí)鐘電路時(shí)不考慮這種因數(shù),則系統(tǒng)動態(tài)性能不會好。這與前端模擬輸入電路的質(zhì)量或變換器的固有抖動性能無關(guān)。精確的時(shí)鐘在精確的時(shí)間間隔總能提供沿轉(zhuǎn)換。

實(shí)際上,時(shí)鐘沿在連續(xù)變化的時(shí)間間隔到達(dá)。因此,這種定時(shí)的不確定性,可以借助數(shù)據(jù)變換過程綜合評估采樣波形的信噪比。

最大時(shí)鐘抖動由下式確定:

Tj(rms)=(VIN(p-p) /VINFSR)×(1/(2(N+1)×π×fin)

假若輸入電壓(VIN)等于ADC的滿標(biāo)范圍(VINFSR),則抖動要求變?yōu)锳DC分辨率(N位)和被采樣輸入頻率(fin)的因數(shù)。

對于70MHz 輸入頻率,總抖動要求是:

Tj(rms)=1× (1/215π×70×106))

Tj(rms)=140fs

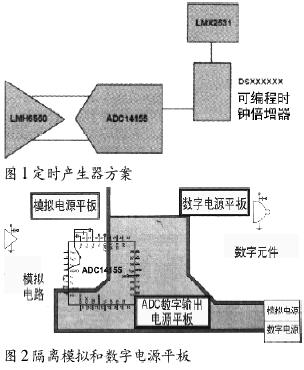

由于很多系統(tǒng)通過背板或另外連接分配參考時(shí)鐘,這會降低信號質(zhì)量,所以,通常用本機(jī)振蕩器(低相位噪聲的VCXD)做為ADC的定時(shí)源。圖1示出用NS公司的LMX2531時(shí)鐘合成實(shí)現(xiàn)定時(shí)產(chǎn)生。連接到定時(shí)產(chǎn)生器的LMX2531由可編程分頻器合成器輸出,給出小于100毫微微秒的抖動性能。

評論