基于FPGA的DDR SDRAM控制器在高速數據采集系統中的應用

引言

本文引用地址:http://www.104case.com/article/81674.htmDDR SDRAM是Double Data Rate SDRAM的縮寫,即雙倍速率同步動態隨機存儲器。DDR內存是在SDRAM內存基礎上發展而來的,能夠在時鐘的上升沿和下降沿各傳輸一次數據,可以在與SDRAM相同的總線時鐘頻率下達到更高的數據傳輸率。

本設計中采用Altera公司Cyclone系列型號為EP1C6Q240C8的FPGA實現控制器,以Hynix公司生產的型號為HY5DU121622B(L)TP的DDR SDRAM為存儲器,完成了對數據的高速大容量存儲。

DDR SDRAM的控制原理及存儲功能的實現

DDR SDRAM支持的常用命令有7種:空操作(NOP)、激活操作(Active)、突發讀(Burst Read)、突發寫(Burst Write)、自動刷新(Autorefresh)、預充電(Precharge)、模式寄存器配置(Mode Register Set)。所有的操作命令都是通過信號線RAS_N、CAS_N、WE_N共同控制來實現的。

在對DDR SDRAM進行存取數據操作之前,首先要對其初始化,即設置DDR SDRAM的普通模式寄存器和擴展模式寄存器,確定DDR SDRAM的工作方式,這些設置包括突發長度、突發類型、CAS潛伏期和工作模式以及擴展模式寄存器中的對DDR SDRAM內部延遲鎖定回路(DLL)的使能與輸出驅動能力的設置。

初始化完成之后,DDR SDRAM便進入正常的工作狀態,此時便可對存儲器進行讀寫和刷新。DDR SDRAM在一對差分時鐘的控制下工作。命令(地址和控制信號)在每個時鐘的上升沿被觸發。隨著數據DQ一起傳送的還包括一個雙向的數據選通信號DQS,接收方通過該信號來接收數據。DQS作為選通信號在讀周期中由DDR SDRAM產生,在寫周期中由存儲器的控制器產生。該選通信號與數據相關,其作用類似于一個獨立的時鐘,并滿足相應的時序要求。由于DDR SDRAM的數據接口在時鐘的兩個沿的觸發下工作,其數據寬度是存儲器數據寬度的一半。為實現數據的大容量存儲,設計時采用的是一個控制核同時對兩片DDR SDRAM進行操作,外接數據線的寬度由單片DDR SDRAM的16 位擴展到32位。

對DDR SDRAM的讀和寫操作是基于突發的,即從一個選定的地址單元開始,連續存取已設置長度的地址單元,該長度就是所謂的突發長度。DDR SDRAM提供的可編程的讀或寫的突發長度為2,4或8。數據的存取以一個激活命令(Active)開始,接著便是讀(Burst Read)或寫(Burst Write)命令。與激活命令一起被觸發的地址位用來選擇將要存取的區和頁(或行),與讀或寫命令一起被觸發的地址位用來選擇突發存取的起始列單元。讀命令被觸發后,數據將在1.5~3個時鐘周期之后出現在數據總線上。這個延遲就是所謂的CAS潛伏期(CAS latency),即從DDR SDRAM內核讀出數據到數據出現在數據總線上所需要的時間。CAS潛伏期的大小與SDRAM的速度和存儲器的時鐘頻率有關。當要存取一個不同行的地址單元時,需要通過一個預充電(Precharge)操作關閉當前行。自動刷新(Autorefresh)命令用來周期性地刷新DDR SDRAM,以保持其內部的數據不丟失。

DDR SDRAM控制器的設計

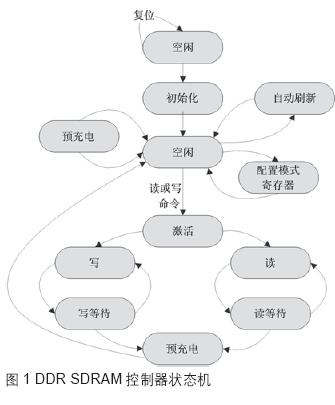

DDR SDRAM控制器的功能包括:(1)初始化DDR SDRAM;(2)簡化DDR SDRAM的讀寫時序;(3)將DDR SDRAM接口的雙時鐘沿數據轉換為單時鐘沿數據,使得對DDR SDRAM的操作類似于普通RAM;(4)控制器還要產生周期性的刷新命令來維持DDR SDRAM內的數據而不丟失。其控制轉換圖如圖1所示。

在對DDR SDRAM初始化完成之后,就可進行讀、寫或其他操作。在執行讀(寫)命令之前,先要激活將要讀(寫)的行,之后便可對該行進行突發讀(寫)。在控制器的設計中,所有的讀寫命令都是不帶預充電的,因此,某一行被激活之后將一直處于激活狀態,直到用戶發送突發終止命令,此時控制器將自動產生一個預充電命令來關閉當前行。這樣,某一行被激活之后用戶便可進行連續的突發讀(寫)操作,從而節省了每次突發讀寫所需要的激活時間,提高了系統的數據吞吐率。

DDR SDRAM的讀操作流程

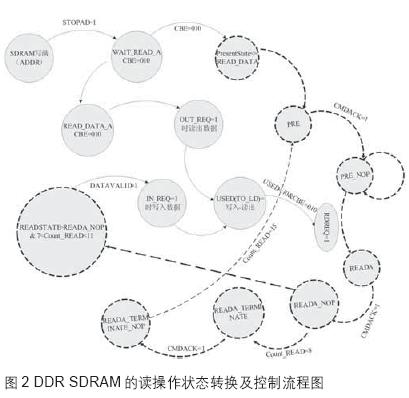

通過對DDR SDRAM的讀時序的分析,將整個讀操作過程分解為7個狀態,每一個狀態都對應著不同的命令(CMD)值,DDR控制核通過對CMD的譯碼完成對DDR SDRAM的操作。從整體的控制過程來看,讀操作流程如圖2所示。其中實線表示的是讀操作的控制流程,虛線表示的讀操作的狀態轉換流程。控制流程的實現依賴于控制器內部狀態轉換產生的控制信號。實現各狀態之間切換的控制信號主要有命令應答信號CMDACK,外部控制信號RDREQ以及程序內部的計數器Count_READ。當系統的主狀態機進入到讀數據狀態時,控制信號CBE=“010”;控制器內部的狀態機進入到讀狀態。讀流程中另一個重要的信號為RDREQ,它是由控制器后端的緩存(FIFO)產生的,當緩存中數據容量低于設定值時,信號RDREQ被置高,讀狀態由PRE_NOP進入READA,發起一次讀操作,完成8個數據的傳送。程序內部的計數器Count_READ保證控制核在經過設定的CAS潛伏期后從數據總線上讀取數據。

DDR SDRAM的寫操作流程

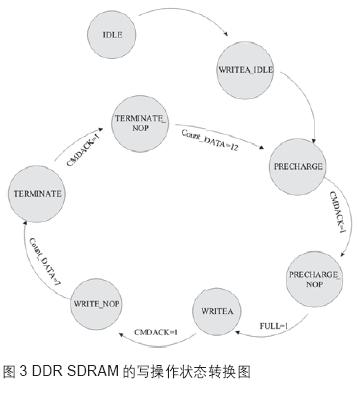

在對DDR SDRAM的寫操作中,同樣以狀態機完成其時序控制,狀態轉換圖如圖3所示。

每發起一次寫操作,DDR SDRAM存儲8 個16位的數據,其中控制信號FULL由前端數據緩存(FIFO)產生,當前端緩存中存儲的數據達到設定的深度時,FULL被置為高,控制核以100MHz的時鐘從緩存中讀取寬度為32位的數據,當緩存內部的讀計數器計數到4時,FULL信號置低,控制器的讀操作停止。讀出的4個32位數據經過控制核內部的數據路徑模塊轉換成DDR SDRAM接口的16位數據格式,在DDR控制接口模塊產生的時序配合下以雙倍速率完成一次突發寫。

DDR SDRAM控制器的FPGA實現

控制電路主狀態機設計

主狀態機用于控制整個數據采集系統的工作流程。各功能模塊的配合,命令的發送,數據的采集、存儲和傳輸都需要狀態機來協調并嚴格控制時序關系。其狀態轉換圖如圖4所示。

控制器上電或復位時進入IDLE 狀態,其中LA和LD分別為PCI局部總線的地址線和數據線,上位機的發送的命令通過PCI總線及接口芯片傳送到PCI局部總線,其中地址線的變化將引起狀態機內部的狀態轉換,狀態轉換的同時,相應的配置字將出現在數據線上。配置完參數之后,轉態機進入等待數據狀態(WAIT_DATA),當觸發信號滿足要求之后(TRG=‘1’),自動進入到保存數據狀態(SAVE_DATA),在此狀態下,控制程序開始進行數據采集。指定存儲深度的數據采集完成后,主狀態機自動進入等待讀數據狀態,在接受到地址線上的狀態轉換命令后,分別進入讀取A通道和B通道數據的狀態。數據讀完之后,上位機發送命令使狀態返回到IDLE狀態。

DDR SDRAM控制器各模塊結構圖

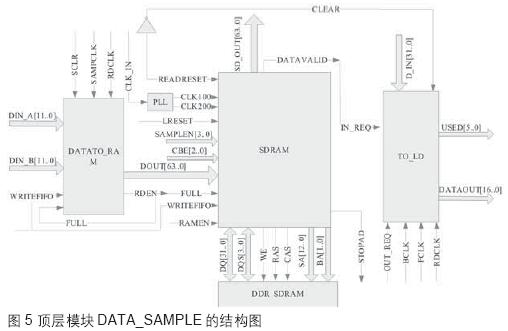

系統的頂層文件DATA_SAMPLE的結構如圖5所示,FPGA內置的主要有前端緩存模塊DATATO_RAM、后端緩存模塊TO_LD和DDR SDRAM的控制模塊SDRAM。從數據流程上看,前端緩存將雙路AD采集到的數據合并成64位,當緩存中的數據達到設定的存儲深度時,控制模塊在100MHz的時鐘下將數據讀出,并將64位數據拆分成32位分別存儲到兩片DDR SDRAM中。進入到讀狀態時,控制模塊同時從兩片DDR SDRAM中讀出32位的數據,根據用戶所選擇的數據通道,控制邏輯將相應的數據送入后端緩存中,后端緩存再將數據拆分成16位,通過PCI局部總線傳送到上位機中。從控制流程上看,DATATO_RAM和TO_LD中都設置了數據計數器,當DATATO_RAM中存儲的數據量超過設定值時,讀使能RDEN有效,控制模塊從緩存中一次讀取4個數據。后端緩存的控制方式與此類似。

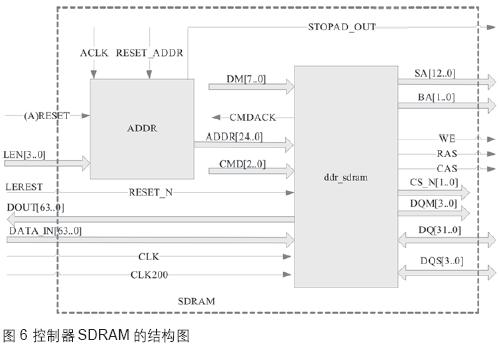

控制模塊SDRAM 由兩部分組成,其結構如圖6所示。其中ADDR為地址產生模塊,給控制核ddr_sdram提供數據操作的行地址和列地址。控制核ddr_sdram完成的功能包括將內部狀態轉換產生的CMD控制命令譯碼成DDR SDRAM所能實現的各種操作并實現以雙倍的速率與DDR SDRAM進行數據交換的接口。ddr_sdram的結構框圖如圖7所示。

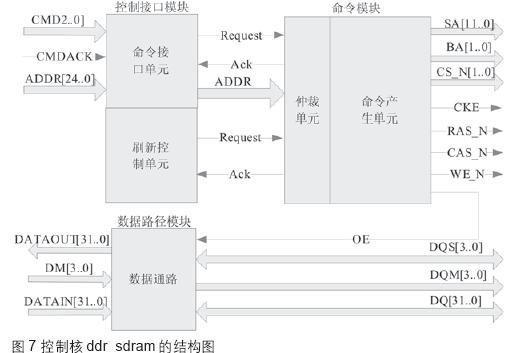

控制核ddr_sdram采用自頂而下模塊化的設計方法,由4個模塊構成:ddr_sdram頂層模塊、控制接口模塊、命令模塊和數據路徑模塊。ddr_sdram頂層模塊初始化并把其余三個模塊有機地結合起來;控制接口模塊接收CMD命令和相關存儲器地址,對命令進行譯碼并將請求發送給命令模塊;命令模塊接收從控制接口模塊譯碼后的命令和地址,產生相應的命令給DDR SDRAM;數據路徑模塊在讀命令READA和寫命令WRITEA期間處理數據交換。

控制接口模塊包含1個命令譯碼器和1 個16 位的刷新減計數器及相應的控制電路。 命令譯碼器譯碼并將譯碼后的命令及相應的地址轉送給命令模塊。減計數器和相應的控制電路用來產生刷新命令給命令模塊。其值就是由LOAD_REG2 命令寫入到REG2中的值。當計數器減到0時,控制接口模塊就向命令模塊發Request 并一直保持到命令模塊發Ack來響應該請求。一旦控制接口模塊接收到Ack,減計數器就會重新寫入REG2中的值。

命令模塊由1個簡單的仲裁器、命令發生器及命令時序器組成。它接收從控制接口模塊來的譯碼后的命令,同時接收刷新控制邏輯發來的刷新請求命令并產生正確的命令給DDR SDRAM。仲裁器在控制接口發來的命令和刷新控制邏輯發來的刷新請求命令之間進行仲裁。刷新請求命令的優先級高于控制接口來的命令。在仲裁器收到命令譯碼器發來的命令后,該命令就傳送到命令發生器,命令時序器即用3個移位寄存器產生正確的命令時序后發給DDR SDRAM。1個移位寄存器用來控制激活命令時序,1個用來控制READA和WRITEA命令,1個用來計時操作命令的持續時間,為仲裁器確定最后的請求操作是否完成。

數據路徑模塊提供了DDR SDRAM到FPGA的數據通道。在和DDR SDRAM接口的一方,數據路徑模塊將從DDR SDRAM過來的數據總線寬度翻倍,并在200MHz的時鐘頻率接收DDR SDRAM在100MHz時鐘的上下沿送出的數據。在和FPGA接口的一方,數據路徑模塊將從FPGA送來的數據寬度減半并以2倍的速率送給DDR SDRAM。

系統實現的功能及結果分析

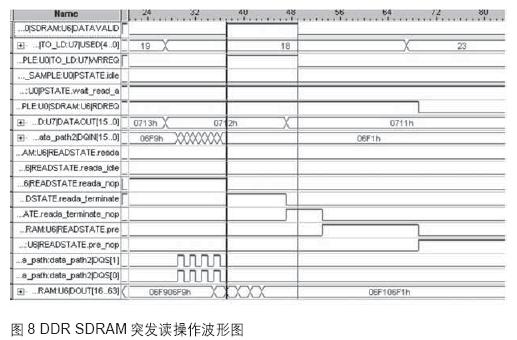

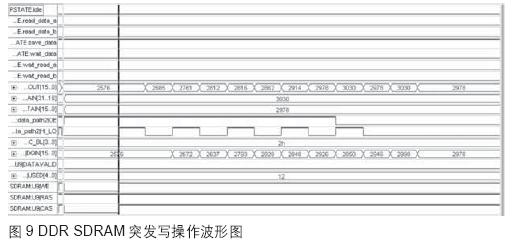

邏輯分析儀SignalTap II是Quartus II軟件中集成的一個內部邏輯分析軟件,使用它可以觀察本設計的內部信號波形。在系統的軟件設計和仿真完成之后,將編譯后的文件下載到系統的硬件中,對DDR SDRAM控制器的狀態轉移和讀寫流程中各個信號進行了實時的采集與顯示。

如圖8所示,是控制器讀數據時嵌入式邏輯分析儀采集到的波形圖。第9行到第15行的信號顯示的是讀流程中各狀態之間的切換過程。讀命令發出之后,經過CAS潛伏期,DDR SDRAM突發傳輸8個數據,并產生選通信號DQS。控制器在讀到數據線DQ上的數據后,將數據寬度加倍,傳送到后端緩存中。

寫數據的波形圖如圖9所示,當主狀態機在SAVE_DATA狀態時,DDR SDRAM從控制器的數據總線上一次存儲8個數據。圖中的選通信號HI_LO是由控制器產生的,在信號的上升沿和下降沿存儲器存儲數據總線上的數據,存滿8個完成一次寫操作。直到前端緩存的讀使能信號有效時,控制器從前端緩存讀取數據,并發起下一次寫操作。

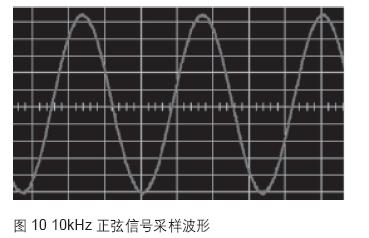

將所設計的控制器用于最高采樣速率為10MHz的數據采集系統中,DDR SDRAM工作的差分時鐘為100MHz,容量為32MByte,系統運行性能良好,能夠較好的完成DDR SDRAM與AD轉換模塊,PCI總線接口模塊之間的數據交換。圖10為數據采集卡對10kHz正弦信號采樣的波形。

結語

本設計在深入了解DDR SDRAM工作原理的基礎上,確定了DDR SDRAM控制器的總體方案和模塊化設計方法。用FPGA實現的DDR SDRAM的控制器能在很高的速度下完成數據的讀寫和復雜的控制操作,工作可靠。該控制器解決了DDR SDRAM用于高速數據采集的關鍵技術問題,對增加數據采集系統的緩存容量具有一定意義。

存儲器相關文章:存儲器原理

塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論