微處理器和JTAG總線橋接接口(06-100)

數(shù)字邏輯設(shè)計(jì)人員在實(shí)現(xiàn)設(shè)計(jì)目標(biāo)時(shí)有不少工具可用。為適應(yīng)所需的大量邏輯數(shù)和數(shù)據(jù)率,設(shè)計(jì)人員可選用FPGA。FPGA在相對(duì)小的空間內(nèi),以多引腳數(shù)封裝提供巨大數(shù)量的數(shù)字邏輯門(mén)。

本文引用地址:http://www.104case.com/article/81431.htm在印刷電路板(PCB)放置多個(gè)多引腳FPGA和其他器件,確保所有互連的完整無(wú)損是比較困難的。在制造中用X射線技術(shù)可以檢驗(yàn)大概的互連問(wèn)題, 而需要更精確的方法來(lái)檢測(cè)制造、調(diào)試和復(fù)雜PCB更換的互連問(wèn)題。

一種方法是JTAG(IEEE1149.1)技術(shù)。JTAG(聯(lián)合測(cè)試行動(dòng)組)功能包括基本的輸入/輸出邊界掃描控制(由1149.1規(guī)范確定)以及內(nèi)部資源的重新編程性和控制。數(shù)字設(shè)計(jì)中所用的很多元件都具有JTAG性能。微處理器可用JTAG提供調(diào)試接入。FPGA和CPLD可用JTAG編程。這些JTAG性能為制造、設(shè)計(jì)和服務(wù)人員提供一個(gè)強(qiáng)有力的生產(chǎn)高質(zhì)量板的工具。

在系統(tǒng)中實(shí)現(xiàn)JTAG控制邏輯時(shí),考慮DFT(design-for-test),而這與一般的FPGA設(shè)計(jì)技術(shù)是矛盾的。

DFT設(shè)計(jì)考慮包括:

·主要的測(cè)試/調(diào)試能力必須與系統(tǒng)開(kāi)發(fā)每個(gè)階段的FPGA功能無(wú)關(guān)。

·FPGA需要在現(xiàn)場(chǎng)更新測(cè)試控制邏輯,并且在重新編程期間應(yīng)變得不起作用。假若希望系統(tǒng)是“5個(gè)9”(99.999%)可用的,則需要另一種FPGA結(jié)構(gòu)。

·FPGA通常是JTAG掃描鏈的部分,而且感興趣的是FPGA互連的檢驗(yàn)。FTAG控制邏輯不能置FPGA進(jìn)入測(cè)試模式,并同時(shí)工作在非測(cè)試模式。

一個(gè)小的定制非易失性的即時(shí)接通可編程邏輯(PLD)能很好的適合系統(tǒng)DFT考慮。這樣的一種器件可提供足夠的邏輯和足夠的I/O組,使其容易調(diào)試和接口到JTAG,以便提供測(cè)試性、重新可編程性的控制功能性。這使得小的PLD成為板測(cè)試無(wú)故障的理想元件。

典型的PCB測(cè)試結(jié)構(gòu)

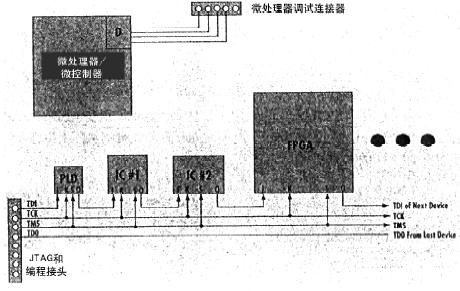

JTAG的主要用途集成在制造測(cè)試。它對(duì)開(kāi)發(fā)環(huán)境有損害,它主要是處理任務(wù)而不是制造級(jí)連接性測(cè)試。圖1示出典型的PCB測(cè)試結(jié)構(gòu)。

評(píng)論