外形似集成電路的完整 DC/DC 解決方案為基于 FPGA 的系統帶來切實益處

FPGA 工藝尺寸的進步和更加靈活的設計配置、以及基于 FPGA 的系統取得的進步已經使 FPGA 制造商充滿信心地進入了以前由微處理器和 ASIC 供應商壟斷的市場。最近,Xilinx 的 VirtexTM 和 Altera 的 Stratix產品系列分別推出了新器件,進一步縮小了性能差距,再次提高了性能標準。盡管這些器件的通用和可配置性吸引了系統設計師,但是控制這些器件內部工作方式的設計規則及其外部接口協議的復雜性導致需要廣泛的培訓、基準設計評估、設計仿真和驗證。因此,FPGA供應商提供了詳盡的硬件和固件支持,旨在幫助系統設計師應對數字領域中的全新挑戰。然而,模擬領域(特別是用于內核、I/O、存儲器、時鐘及其它電源軌的DC/DC轉換器)中難解的復雜性則需要新型解決方案。現在,是 DC/DC 制造商提高自己產品性能標準的時候了。

本文引用地址:http://www.104case.com/article/81394.htm 管理多個電壓軌

較舊的 FPGA 需要兩個或 3 個電源軌。現在,有些高端多核器件需要多達 7 個軌,兼有 3.3V 舊的電源軌和新近出現并從 2.8V 直至 1.0V 或更低的較低電壓軌。此外,還兼有為存儲器、網絡處理器、圖形處理器、數摸或模數轉換器以及運算放大器和射頻集成電路等非 FPGA 器件提供的其它電壓軌。

確保具有多個電壓軌的系統“清楚”啟動、電壓軌相互之間沒有任何沖突是具有排序和跟蹤功能的 DC/DC 穩壓器的關鍵任務。簡言之,每個穩壓器必須能夠跟蹤其它穩壓器的輸出電壓。好消息是,從幾年前開始,FPGA 就不需要對其電壓軌進行任何排序了。但是仍然要求系統中不同部分的幾個電壓順序斜坡上升或斜坡下降,以防止電壓軌變化太快或太慢時可能出現鎖斷。

過去,電源軌的跟蹤和排序由單獨的電源管理集成電路完成。今天,設計師要求排序和跟蹤功能嵌入到穩壓器中,尤其是穩壓器必須放置在系統中不同的角落時,更是這樣。

調節低 Vt 和極快的大電流 I/O

在基于 FPGA 的應用中,快速 I/O 節點常常需要最高功率。1.8V 至 2.5V I/O 電壓產生數十安培的負載電流是非常常見的。非常高端的系統需要 40A 至 80A 的 I/O 設計。

由于電路板設計的邏輯學原因,DC/DC穩壓器不得不布設在遠離其負載的地方,并需要在其輸出至調節點之間采用一根很長的PCB印制線。在大負載電流時,印刷電路板走線引入電壓誤差,大小等于負載電流(I)乘以這段走線的阻抗(R)。這個 I×R 電壓誤差成了較大的問題,因為負載電壓一直在下降,而負載電流一直在上升。例如,對一個 3.3V 軌,200mV 的 I×R 壓降產生 6% 的誤差,而對一個 1.2V 軌,則引入 17% 的誤差。因此,盡管 DC/DC 穩壓器可以設置為調節 1.2V 輸出,但是由于 I×R 壓降,負載將僅得到 1.0V。

采用今天的 90nm 和 65nm 工藝時,Vt 和 FPGA 的性能取決于電源軌的精確度,17% 的誤差可能非常容易使性能降低。例如,Vt 中出現 100mV 的偏差可能導致漏電流擴大 10 倍或更多(1)。

只有負載非常接近穩壓器輸出時,標準 DC/DC 穩壓器才能實現精確調節。它無法補償 I×R 壓降。誤差校正必須借助遠端檢測放大器進行。用差分遠端負載檢測可以實現最嚴格的調節,這需要一個精確的運算放大器和精確電阻。一個放置在負載處的理想穩壓器即使在 –40oC 至 85℃的溫度范圍內也應該提供高于 ±1.5% 的調節準確度。這樣的準確度對于 3.3V 電源軌而言也許無關緊要,因為這時數字集成電路可以容許 ±0.5V 的變化,但是具有 1.8V、1.0V 或 0.9V 電源軌的 90nm 或 65nm 器件將需要更高的準確度。

用戶一旦設定了穩壓器輸出電壓,差分遠端檢測就通過在寬負載電流范圍內補償印刷電路板走線上的 I×R 壓降,自動調節負載點處的穩定電壓。結果,系統在備用模式或在負載電流和 I x R 壓降都為峰值的全速工作狀態時,調節都非常準確。

降低對電壓紋波噪聲和電容器的要求

在非便攜式應用中,由于所需的電壓降低,而所需電流提高,因此在選擇 DC/DC 穩壓器時,熱量和工作效率成了更重要的因素。在便攜式應用中,盡管每軌負載電流較低,但是工作和備用效率在節省電池能量、簡化便攜式產品熱量管理方面仍然發揮著重要作用。

與線性穩壓器相比,無論是便攜式還是非便攜式應用,開關模式 DC/DC 穩壓器都可組成較高性能的解決方案,尤其是需要大功率時更是這樣。例如,一個用 3.3V 輸入電源、以 90% 效率提供 1.2V/5A 輸出的開關模式穩壓器與一個效率為 36% 的線性穩壓器相比;另外,開關模式穩壓器消耗 0.7W 功率時,線性穩壓器消耗 10.5W。

另一方面,開關模式穩壓器因其固有的開關工作而引入開關噪聲和較高的輸出紋波噪聲(輸出電壓峰值至峰值紋波)。不幸的是,新型 FPGA 的較低電壓軌和較快 I/O 信號更嚴格的眼圖只容許較低的電源“噪聲”。為了減輕紋波噪聲,可以給電路增加更多輸入和輸出電容器,以降低峰值至峰值紋波電壓。不過,降低開關噪聲難度更高。一種可能的方法是使DC/DC穩壓器的工作頻率與一個外部時鐘相同步,這將使穩壓器在所選擇的設定頻率范圍之內運作,以最大限度地降低對系統中其它對噪聲敏感的器件的干擾。在幾個開關模式穩壓器都同步到一個對系統其余部分而言是安全的時鐘頻率時,這種方法尤其有效。

這些方法有助于設計較低噪聲的開關模式負載點穩壓器,不過,如果 DC/DC 穩壓器以恰當的架構、功能和布局從頭設計,那么噪聲問題可以大大減輕。這樣的穩壓器最大限度地減輕了對電容器、濾波和EMI(電磁干擾)屏蔽的依賴。

在系統質檢和組裝時精調電壓

FPGA 或支持 FPGA 的集成電路的性能在組裝進完整的系統時和在實驗臺上單獨測試時相比,可能有所不同。焊料類型、溫度、印刷電路板布局、走線阻抗、組裝流程等因素都會影響到一個組件的性能。例如,如果 FPGA 內核穩定在非預期電壓上而且導致較慢的速度,那么系統的計算能力將下降。在有些情況下,質量控制人員必須拒絕接受一個偏離預期性能的系統。

由于這個原因,工程師在質檢或組裝期間評估性能時,需要能夠以小的增量提高或降低輸出電壓。這個功能叫裕度控制。在前面的例子中,可能提高內核電壓,以便 FPGA 的工作頻率達到需要的值。裕度控制功能在生產時還可以幫助系統制造商提高總產量。

降低高度以讓空氣更好地流動

縮小 FPGA 系統尺寸同時增加功能、存儲器存儲容量或計算能力的迫切需求促使設計師改進用來冷卻組件的方法。一種簡單的方法是在組件上面提供充足的空氣流動。較高的組件遮擋了 FPGA 或存儲器集成電路等較薄封裝上面的空氣流動。在預裝配 DC/DC 負載點穩壓器情況下,這種遮擋非常嚴重,因為這類器件的高度達到了 FPGA 和其它集成電路高度的 6 至 10 倍。

在把封裝內部產生的熱量從封裝頂部有效散逸出去的過程中,FPGA扁薄的BGA封裝是極有幫助的。而在采用較高的器件(例如:預制的DC/DC穩壓器)時,由于它阻礙了氣流的流動并對相鄰的器件產生了“遮蔽”,因此導致上述好處大打折扣。

新一代 DC/DC 系統:微型模塊穩壓器

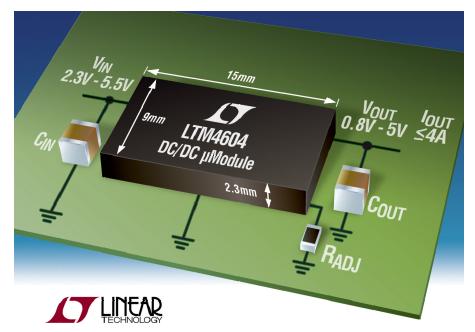

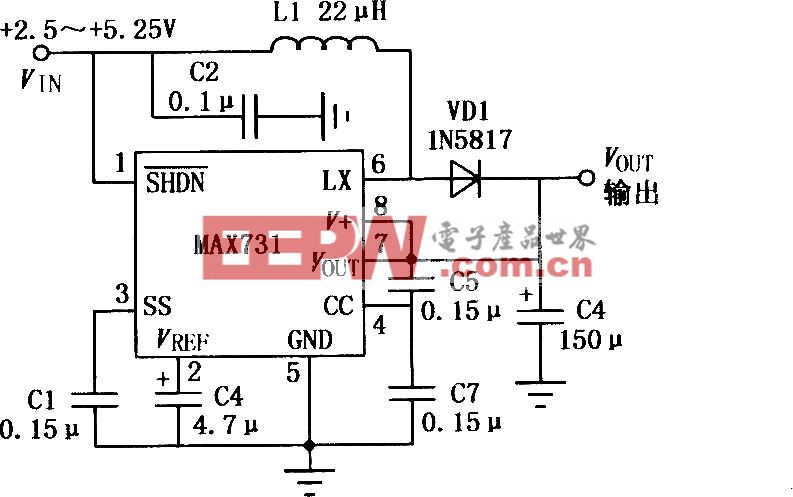

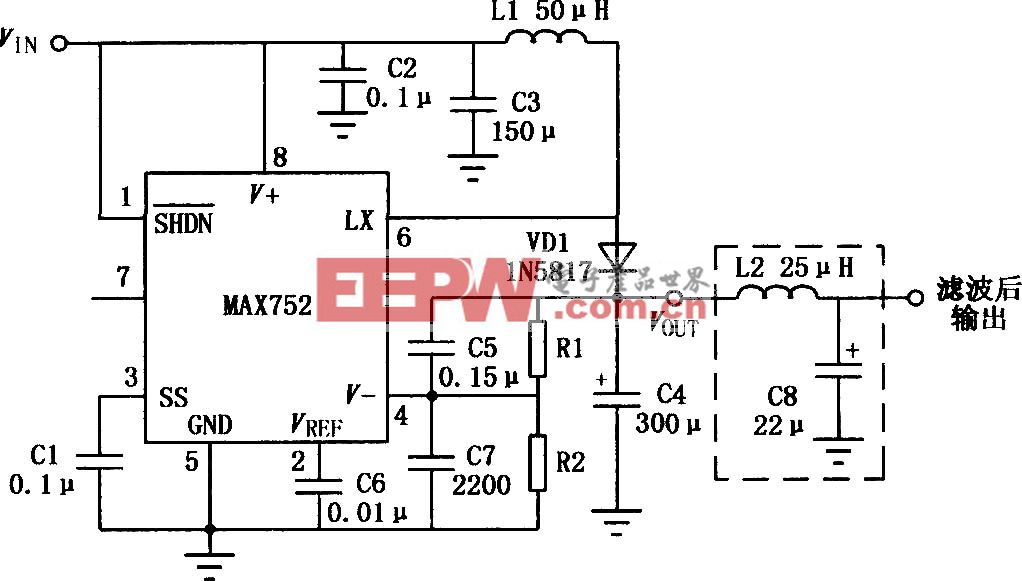

我們來看一個完整的開關模式 DC/DC 系統,其中包括片上 MOSFET、電感器、電容器、DC/DC 控制器和補償電路,裝在一個類似表面貼裝集成電路那樣的封裝中,具有簡單的布局,僅需要少數幾個大容量電容器和一個電阻來設置輸出電壓(圖 1)。為實現最佳電氣和熱性能,這個 DC/DC 系統可以在充分注意布局和封裝的情況下進行預組裝。該 DC/DC 開關模式架構可以采用具有快速瞬態響應的電流模式架構,以最大限度縮小輸出電容器尺寸。該 DC/DC 系統可同步至外部時鐘,幾個系統可以并聯以提供大電流,同時最大限度降低開關噪聲干擾和輸出紋波噪聲。這種新一代 DC/DC 穩壓器應該密封在一個小的、重量很輕的表面貼裝封裝中,以實現更緊湊和更簡單的電路板組裝。該封裝的高度應該很低,允許空氣非常容易地在自身及其附近的集成電路周圍流動。

圖 1 像線性穩壓器一樣簡單:一個 DC/DC 微型模塊穩壓器就是一個密封的表面貼裝解決方案,具有電感器、MOSFET、DC/DC 穩壓器和補償電路

凌力爾特公司將這種新一代 DC/DC 系統稱為微型模塊(μModule)穩壓器,包括一系列器件,輸出電流范圍為 6A 至 16A,輸入電壓范圍為 4.5V 至 28V,輸出電壓范圍為 0.6V 至 5V(表1)。有些功能豐富的微型模塊穩壓器還具有跟蹤功能,以使多個電源軌 FPGA 系統實現恰當的啟動和停機。甚至電感器也是屏蔽的,以最大限度降低 EMI。有了裕度控制功能,系統設計師就可以準確調節電壓,這樣,除了在組裝和測試時提高產量,還可提高 FPGA 和系統其余部分的性能。

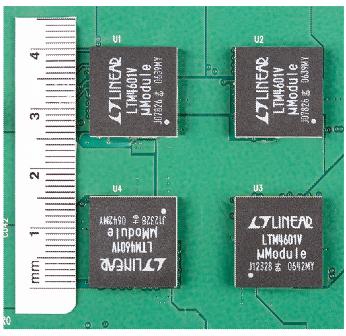

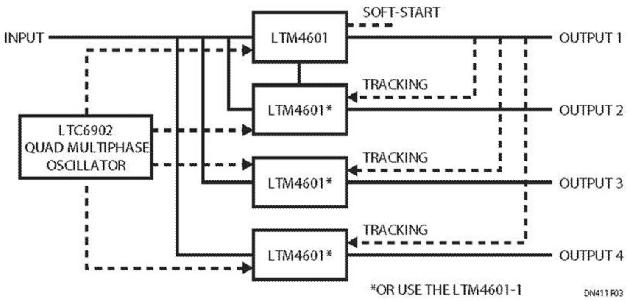

圖 2 顯示了一個采用 LTM4601、在 4 層印刷電路板上設計的 4 輸出 103W 微型模塊 DC/DC 系統。該解決方案用 8V 至 16V 的中間總線輸入提供 1.5V/12A、1.8V/12A、2.5V/12A 和 3.3V/10A 四個輸出。這個設計的簡化方框圖如圖 3 所示。4 個 LTM4601 單元的相位鎖定至 4 輸出、4 相振蕩器 LTC6902,該振蕩器產生以 90o 交錯的時鐘信號,以降低噪聲和紋波。

圖 2 一個 4 輸出 103W DC/DC 系統可以放進這個纖巧的空間中(每個 LTM4601 微型模塊 DC/DC 轉換器都包含一個電感器、MOSFET、旁路電容器 … 等等)。

圖 3 圖 2 的簡化方框圖

結語

凌力爾特公司在 DC/DC 穩壓器架構和封裝領域的創新已經允許新一代負載點解決方案滿足 FPGA 系統更嚴格的要求。微型模塊 DC/DC 穩壓器系列(表 1)由 6 個具有不同功率級和功能的產品組成(請訪問網址:www.linear.com..cn/micromodule)。這些器件的可靠性在多芯片封裝領域也豎立了新的標準,并得到凌力爾特公司嚴格的質檢和測試支持。這些微型模塊 DC/DC 解決方案為新一代 FPGA 和基于 FPGA 的系統更精細地提高性能創造了機會。

表 1 用于 FPGA 系統的纖巧 DC/DC 微型模塊產品

評論