時鐘技術的未來發展:向分組網絡轉型(06-100)

——

線路卡上 PLL(DPLL、APLL 或數字與模擬 PLL)的主要要求是監控來自時鐘卡的系統時鐘并在發生故障時執行無中斷參考轉換。線路卡上的 PLL 還必須執行抖動衰減,從而為線路卡器件提供低抖動時鐘,以確保操作無故障并符合相關標準。

本文引用地址:http://www.104case.com/article/81182.htm如前所述,線路卡上的 PLL 鎖定于來自時鐘卡之一的背板參考時鐘,隨后其還將為 TSI、成幀器和 LIU 生成線路卡上所有必需的頻率。上述頻率通常分別為 8 kHz、1.544 MHz 和 2.048 MHz。我們假定背板參考時鐘頻率為 8 kHz 和 2 MHz。

線路卡還能從T1/E1線路提取時鐘參考,并將其提供給時鐘卡。通常它會是8 kHz的頻率參考。

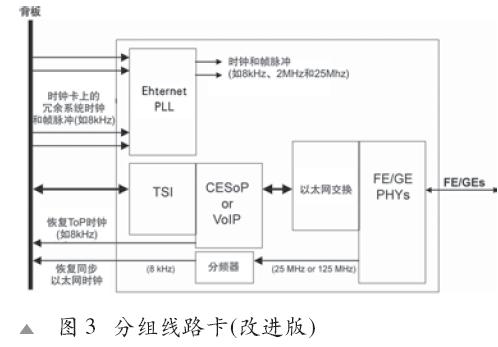

分組線路卡(改進版)

圖3 給出了一款簡化線路卡,該線路卡不僅具有以太網接口,而且還能滿足傳統 TDM 線路卡現有系統背板設置的要求。背板的時鐘和數據接口保持不變。NxDS0數據仍通過 TSI 傳輸,提取的線路卡時鐘以及背板時鐘卡時鐘仍為 8 kHz 和 2 MHz。

不過,就線路卡本身而言,VoIP 或 CESoP (電路仿真分組業務)處理器協同以太網交換機與 FE/GE PHY 在以太網/IP網絡上傳遞 NxDS0 語音服務。

評論