基于嵌入式TCP/IP軟件體系結構的優化設計與實現(06-100)

——

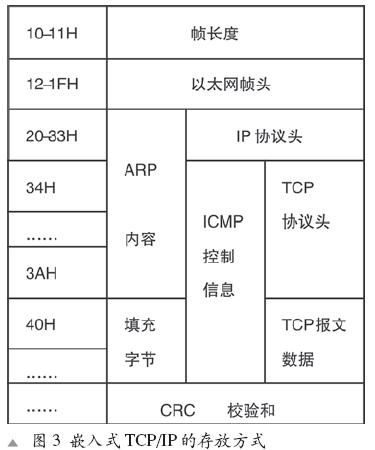

為了減小RAM使用量,當數據包需要重新發送時,如果能夠重新產生數據包所需的數據,可以不存儲需要被應答的TCP包。圖3給出了嵌入式CPU中TCP/IP的內存劃分,以及內存中幀的各個字節的定義和相對位置,其中PacketRAM為存放幀的首地址。

發送TCP/IP過程中主要的運算量集中在三個部分:應用程序將數據拷貝到RAM、計算TCP校驗和、將RAM中的數據包拷貝到網絡設備的發送緩沖區。對每一個字節數據,兩次拷貝大致共使用12×2=24個指令周期;計算TCP校驗和使用為16個指令周期。為提高速度可采用快速CPU或提高晶振頻率。例如采用12M晶振時,網絡傳輸速度為25K字節/s;而在高頻PCB電路板使用233M晶振時,網絡傳輸速度能達到為384K字節/s。

tcp/ip相關文章:tcp/ip是什么

評論