采用FPGA協處理器優化汽車信息娛樂和信息通信系統(04-100)

由主處理器控制專用硬件加速器,一般通過寄存器和存儲接口實現,每個寄存器控制部分硬件加速器的運行。這適用于Delphi系統的默認協同芯片,也適用于下載到協同FPGA中的協處理器體系。通過使用FPGA可以直接將寄存器和存儲器接口標準化,以控制任何編程實現的協處理器。標準化的接口可以定義怎樣讀取和寫入協處理器數據,怎樣開始和停止這一過程,怎樣進行復位,并包括了一組寄存器實現控制專用操作。所有這些寄存器都是FPGA內線性地址映射的一部分,這樣,軟件物理器件驅動器能夠很容易的讀取寄存器。

本文引用地址:http://www.104case.com/article/80965.htm協處理器的軟件物理器件驅動器與硬件寄存器接口相比,具有更高級的抽象功能。軟件驅動器實現了系統算法參數到控制寄存器的映射,因此可以很容易的編寫和維護應用軟件。底層的硬件改變時,高層的模型器件驅動器可以保持不變。Delphi系統中的軟件體系提出了幾個抽象層,將算法實現從其軟硬件物理實現中分離出來,為軟件或硬件協處理器算法提供了強有力的支持。FPGA協處理器非常適用于這種Delphi軟硬件體系。

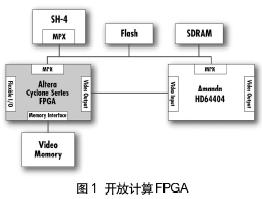

FPGA可以設計應用到許多基本體系和Delphi結構相似的系統中去。這些系統包括一個或者多個控制器或DSP處理器,可以使用FPGA加速實現需要高性能處理的任務。實現FPGA協處理器的關鍵在于為FPGA設計不同的硬件加速器,外部控制處理器集成硬件加速器,產生進行硬件加速控制的軟件層。所需硬件加速器應用包括視頻和通信的主流算法。這些應用有廣闊的市場,已經開始服務于那些致力于設計標準專用知識產權(IP)硬件加速器的專業公司。這類公司提供通用算法,直接應用到先進的低成本FPGA上。可以直接購買商用MPEG2,MPEG4,H.264,WiFi的IP模塊,以及許多其他的視頻和通信標準IP模塊。圖2的例子是Amphion公司的MPEG4解碼器IP模塊,適用于ASIC或FPGA應用場合。

下一步是在FPGA中集成硬件加速器,利用外部總線進行控制,數據輸入和輸出。設計者可以使用一種新的開發工具,很容易的實現這種集成。利用來自Altera的系統集成工具--SOPC Builder,設計者從可用的IP列表中選擇合適的IP模塊。進行選擇時,參數化菜單顯示不同結構的選項,這些選項由使用者在執行前進行設置。設置好參數后,模塊便被包含到別的外設列表中,處理器由工程師進行集成。每個獨立IP模塊被選擇并參數化后,他們將被集成到處理體系中去。

評論