用DSP實(shí)現(xiàn)CPLD多方案現(xiàn)場(chǎng)可編程配置

1 總體描述

系統(tǒng)中的DSP采用TI公司的定點(diǎn)數(shù)字信號(hào)處理器TMS320C5402。它采用4總線4級(jí)流水線的增強(qiáng)型哈佛結(jié)構(gòu),處理速度為100MIPS;具有片內(nèi)4K×16位的ROM和16K×16位的DARAM, 2個(gè)多通道緩沖串行口(McBSP),1個(gè)直接存儲(chǔ)控制器(DMA)等片內(nèi)外圍電路;外部可擴(kuò)展至1M×16位存儲(chǔ)空間,芯片采用3.3V電源電壓。

TMS320C5402的多通道緩沖串行口(multi-channel buffercd scrial port)具備標(biāo)準(zhǔn)串行口的所有功能,可設(shè)定收發(fā)數(shù)據(jù)格式(8位~32位);在8位不擴(kuò)展模式下,可選擇高位(MSB)先送或低位(LSB)先送。直接存儲(chǔ)控制器(DMA)可以實(shí)現(xiàn)數(shù)據(jù)在串行口McBSP和內(nèi)部DARAM間的直接交換, 提高工作效率, 節(jié)省運(yùn)行時(shí)間。

CPLD采用Altera公司FLEX10K系列的EPFl0KIOA7C144-1。可用資源有576個(gè)邏輯單元(LE)、72個(gè)邏輯陣列塊(LAB)、3個(gè)嵌入式陣列塊(EAB)和102個(gè)I/O引腳,電源電壓為3.3V。

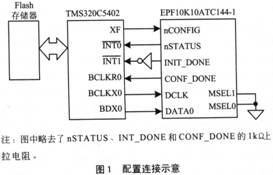

FLEX1OK的配置由Altera的專用串行配置PROM(EPCI)或系統(tǒng)控制器提供的數(shù)據(jù)宋完成,也由編程硬件通過(guò)下載電纜 (BytcBlastcrMV)進(jìn)行在線配置。依據(jù)控制配置過(guò)程的器件不同, 可將配置分為主動(dòng)配置和被動(dòng)配置兩類;依據(jù)配置數(shù)據(jù)流的格式不同,可將配置分為串行配置和并行配置兩類。本文采用的是在微處理器控制下的被動(dòng)串行配置(passivc serial)模式。配置連接示意如圖1所示。

其中,DSP的XF作為輸出控制CPLD的nCONFIG,INTO和INT1作為輸入監(jiān)控CPLD的nSTATUS和1NT DONE,緩沖串行口的BCLKX0和BDX0分別接CPLD的DCLK和DATA0,BCLKR0 作為輸入端檢測(cè)CONF DONE的信號(hào)。TMS320C5402和EPFl0KIOATC144-1都采用3.3V電源電壓。

2 配置數(shù)據(jù)的獲取和存儲(chǔ)

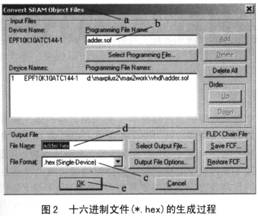

對(duì)CPLD的配置設(shè)計(jì)完成以后,MAX+PLUS II的編譯器在編譯過(guò)程中自動(dòng)產(chǎn)生一個(gè)存儲(chǔ)器目標(biāo)文件(*.sof)。它包括一個(gè)專用數(shù)據(jù)頭和二進(jìn)制配置數(shù)據(jù),供下載電纜(BvtcBlastcrMV)對(duì)器件進(jìn)行被動(dòng)申行配置時(shí)使用。在存儲(chǔ)器目標(biāo)文件(*.sof)的基礎(chǔ)上,可以生成其它類型配置文件。我們所用到的是十六進(jìn)制文件(*.hex),是ASCII形式的配置數(shù)據(jù)文件。使用MAX+PLUSII生成十六進(jìn)制文圖2十六進(jìn)制文件(*.hex)的生成過(guò)程件(*hex)的過(guò)程,如圖2所示。

①完成編譯之后,從“FILE”菜單中選擇“ConvertSRAM Object Files|…”(圖中a);

②選擇相應(yīng)的配置文件*.sof(圖中b);

③設(shè)定輸出文件格式為.hex(圖中c);

④選擇對(duì)應(yīng)輸出文件•.hex(圖中d);

⑤點(diǎn)擊“OK”確認(rèn)(圖中e)。

然后,在MAx+PLUSII環(huán)境下打開生成的十六進(jìn)制文件(*.hex),便可獲取到ASCIl格式的配置數(shù)據(jù)。將配置數(shù)據(jù)通過(guò)DSP的開發(fā)軟件轉(zhuǎn)化成二進(jìn)制數(shù)據(jù),通過(guò)DSP存入其外部大容量數(shù)據(jù)存儲(chǔ)器(flash memory)中。

EPF10K10ATCl44_1的二進(jìn)制配置數(shù)據(jù)大小約為120000位,即14.6KB。TMS320C5402的內(nèi)部DARAM為16K×16位,外部存儲(chǔ)空間為lM×1 6位,故可存儲(chǔ)數(shù)十個(gè)配置文件。

1NT—DONE一狀態(tài)指示端,配置時(shí)為低,配置數(shù)據(jù)初始化完成后釋放,漏極開路;

DCLK一配置時(shí)鐘信號(hào)端;

DATA0——配置數(shù)據(jù)輸入端。

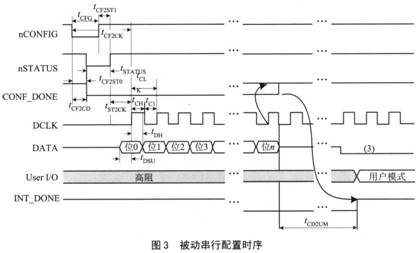

被動(dòng)串行配置(PS模式)的時(shí)序如圖3所示。

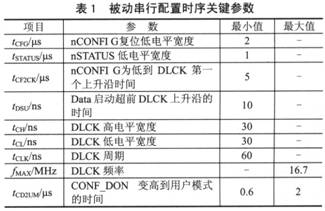

圖3中關(guān)鍵的時(shí)序參數(shù)如表1所列。

3.2配置過(guò)程描述

參照被動(dòng)串行配置時(shí)序,DSP控制下CPLD現(xiàn)場(chǎng)配置的實(shí)現(xiàn)過(guò)程如下所述。

首先,DSP將一個(gè)方案的配置數(shù)據(jù)從外部數(shù)據(jù)存儲(chǔ)器中讀入內(nèi)部DARAM。然后,在DCONFIG上產(chǎn)生一個(gè)由低到高的跳變,使CPLD進(jìn)入配置狀態(tài),等待CPLD釋放nSTATUS。nSTATuS變高之后,通過(guò)McBSP在時(shí)鐘(DCLK)上升沿將配置數(shù)據(jù)逐位送到DATA0上,時(shí)鐘(DCLK)頻率選為10MHz。因?yàn)榕渲靡竺孔止?jié)數(shù)據(jù)的最低位(LSB)先送出,故在初始化McBSP時(shí),設(shè)定發(fā)送控制寄存器(XCRl和XCR2),使McBSP工作于8位不擴(kuò)展傳送模式和低位(LsB)先發(fā)模式,DMA完成數(shù)據(jù)從DARAM到

McBSP口的直接傳送。CPLD接收完所有配置數(shù)據(jù) (120 000字節(jié))后,會(huì)釋放CONF_DONE,變成高電平,之后DSP仍須在DCLK上輸出脈沖來(lái)初始化CPLD器件,直到INT_DONE被釋放變成高電平,表示CPLD器件初始化完畢,進(jìn)入用戶狀態(tài),配置過(guò)程結(jié)束。在配置的過(guò)程中,沒有握手信號(hào)。一旦CPLD檢測(cè)到出錯(cuò),會(huì)將nSTATus拉低,此時(shí)會(huì)產(chǎn)生DSP外部中斷。DSP響應(yīng)中斷后,在nCONFIG上產(chǎn)生一個(gè)由低到高的跳變,重新開始配置,或者DSP檢測(cè)到配置出錯(cuò),也要強(qiáng)制重新開始配置。

配置結(jié)束后,DSP和CPLD將工作于該方案模式下。當(dāng)需要進(jìn)入其它方案模式時(shí),DSP按照需求讀入新的配置方案數(shù)據(jù),對(duì)CPLD重新進(jìn)行配置。由于 DSP的高處理速度(100MIPS)和配置時(shí)鐘的高頻率(10MHz),使得CPLD的配置時(shí)間小于20ms,因此可以快速、靈活地實(shí)現(xiàn)各配置方案間的現(xiàn)場(chǎng)實(shí)時(shí)切換。

結(jié)語(yǔ)

在繼電保護(hù)測(cè)試裝置中,要求測(cè)試端的輸入輸出特性隨被測(cè)試線圈阻抗的變化而改變。CPLD作為測(cè)試端的核心器件,基于DSP實(shí)現(xiàn)其多方案現(xiàn)場(chǎng)可編程配置,實(shí)現(xiàn)了多種類型繼電保護(hù)裝置通用測(cè)試器的設(shè)計(jì)。本設(shè)計(jì)的思路及方法也適用于其它DSP+CPLD/FPGA或MCU+CPLD/FPGA系統(tǒng)。利用系統(tǒng)中現(xiàn)有的DSP/MCU和大容量通用數(shù)據(jù)存儲(chǔ)器,省去專用的配置PROM,方便靈活地實(shí)現(xiàn)對(duì)CPLD的現(xiàn)場(chǎng)可編程配置。

評(píng)論