基于NiosⅡ軟核處理器的七段數碼管動態顯示設計

SOPC(System On Programmable Chip)技術是美國Altera公司于2000年最早提出的,并同時推出了相應的開發軟件Quartus II。SOPC是基于FPGA解決方案的SOC(System On Chip),構成SOPC的方案也有多種。第一種是基于FPGA嵌入IP硬核的SOPC系統,即在FPGA中事先植入嵌入式系統處理器,目前最常用的嵌入式處理器大多采用了含有ARM的32位知識產權處理器核的器件。第二種是基于FPGA嵌入IP軟核的SOPC系統,目前最有代表性的軟核處理器分別是Altera公司的Nios II核,以及Xilinx公司的MicroBlaze核。第三種是基于HardCopy技術的SOPC系統,HardCopy就是利用原有的FPGA開發工具,將成功實現于FPGA器件上的SOPC系統通過特定的技術直接向ASIC轉化。

1 基于Altera公司NiosⅡ軟核處理器的SOPC系統

Altera公司Nios II軟核是目前使用最為廣泛的一種軟核處理器。值得一提的是,利用Matlab和Altera公司的DSP Builder,用戶可以為Nios II軟核處理器設計各類DSP硬件加速器,并以指令的方式加入Nios II的指令集,從而可以構建自己的DSP處理器系統。

1.1 基于NiosⅡ軟核處理器的SOPC系統結構

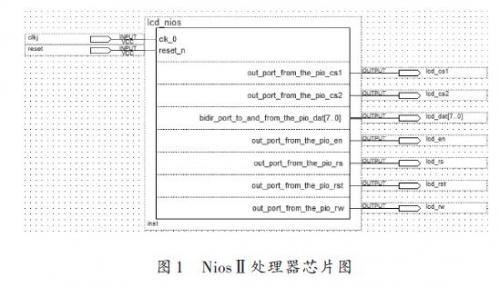

如圖1所示的一個基本的基于NiosⅡ軟核的SOPC系統,除NiosⅡ核、定時器和片上存儲器以外,還需要在FPGA器件中添加一些接口元件。這些元件一方面通過片上的Avolon總線與NiosⅡ軟核相連,另外一方面又提供了外設與NiosⅡ軟核通信的接口界面。

Altera公司QuartusⅡ軟件中的SOPC Builder工具提供了許多常用的外設接口元件,如UART接口元件、PIO接口元件等,通過這些接口元件可以連接諸如RS232、LED、數碼管和按鍵等輸入輸出設備。在相對復雜的系統設計當中,還可以通過Avalon三態總線橋外接大容最的SRAM和FLASH,以提供更大的程序和數據存儲空間。從圖1中,還可以注意到,通過使用系統提供的用戶自定制外設接口元件的功能,用戶可以在系統中添加一個符合Avalon總線規范的外設接口元件,以連接用戶特定功能的外部設備。

1.2 自定制Avalon用戶外設接口元件簡介

對于自定制的Avalon外設接口元件按照Avalon總線操作的不同可以分為兩類:Avalon Slave外設接口元件型的自定制的Avalon Slave外設接口元件框圖。從圖2中可以看到寄存器的定義是自定制外設接口元件很重要的一部分,必須根據設計的需要確定寄存器的個數和種類。圖2中的Avalon Slave接口提供了自定制外設接口元件與NiosⅡ處理器之間數據交換的界面,其接口信號類型也必須根據設計的需要合理地進行選擇。常用的Avalon Slave接口信號類型有:clk,chipselect,address,write,writedata,byteenable,reset等。圖2中的任務邏輯具體說明了自定制外設接口的功能,并給出了與外設連接的接口信號。

自定制Avalon Slave外設接口元件的方法:可以利用SOPC Builder提供的元件編輯器在圖形用戶界面下將用硬件描述語言(Verilog或VHDL)描述的用戶邏輯封裝成一個SOPC Builder元件。相應的硬件描述語言文件給出了自定制外設接口元件的內部寄存器結構,使用到的Avalon Slave接口信號和自定制外設接口的邏輯功能。一旦定制成功后,用戶自定制的外設接口就可以象SOPCBuilder中其他元件一樣被調用。

{{分頁}}

2 基于NiosⅡ軟核處理器的七段數碼管動態顯示設計

數字系統設計中,用數碼管顯示數據結果是常用的一種方法。利用Altera的SOPC Builder工具進行Nios Ⅱ系統設計時,并沒有提供專門的數碼管顯示接口元件,但可以使用PIO元件驅動數碼管顯示,不足之處是占用器件引腳數目過多。本文當中以自定制Avalon Slave外設接口元件的方式,給出了一種基于NiosⅡ軟核的七段數碼管動態顯示設計方案。該設計可以用來驅動1~8個共陰極(或共陽極)數碼管的顯示,可以根據需要選擇小數點顯示的位置,每個數碼管可以顯示0~F之間的十六進制字符。

圖3為自定制的數碼管動態顯示接口元件邏輯結構圖,其中定義了2個寄存器display_data_reg和controlreg。display_data_reg是個一個32位二進制的數據寄存器,其數據每4位可以譯碼得到1個數碼管的七段顯示所需的字符碼,因此,display_data_reg同時最多可以給出8個數碼管所需要的顯示數據。control_reg是一個8位二進制的控制寄存器,但只定義了0~2位和第4位的含義。0~2位的數據給出了小數點顯示的位置,數值范圍在“000”~“111”之間,對應著8個數碼管最低位到最高位的小數點的位置。第4位是數碼管顯示的啟動停止位,當該數據位為1時,可使自定制接口元件所驅動的數碼管正常顯示結果;當該數據位為0時,停止顯示,所有被驅動的數碼管熄滅。

參數n定義了循環加法計數器的模數,同時也決定了驅動數碼管顯示的個數,其取值范圍在1~8之間。clkdisplay是循環加法計數器的時鐘輸入,他決定了計數器的計數頻率,同時也決定了數碼管顯示的動態掃描頻率。參數pos用于決定驅動數碼管的類型,其值可設定為0或1。當其值為0時,seg_out字符碼輸出高電平有效,bit_control數碼管位選控制輸出低電平有效,此時輸出結果用于驅動共陰極數碼管顯示;當pos值為1時,seg_out字符碼輸出低電平有效,bit_control數碼管位選控制輸出高電平有效,此時輸出結果用于驅動共陽極數碼管顯示。

seg_out為自定制元件的字符碼輸出,用于驅動數碼管顯示(包括小數點位)。其中,最高一位seg_out[7]用于驅動對應數碼管的小數點顯示,低7位seg_out[6..0]用于驅動數碼管的七段寧符顯示。圖3中數碼管七段譯碼器根據循環加法計數器的當前狀態值,從display_data_reg寄存器中選擇4位二進制數據進行譯碼。例如,當前驅動的數碼管的個數為5個(即n=5),循環加法計數器的當前狀態值用count表示,則count在0~4范圍內變化;若計數器的當前狀態值count為2,則選擇寄存器display_data_reg[11..8]的4位二進制數據進行譯碼,若計數器的當前狀態值count為3,則選擇寄存器display_data_reg[15..12]的4位二進制數據進行譯碼,即總是選擇寄存器display_data_reg[(count+1)

塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論