低Rds(on) P溝道技術

電子設計應用2003年第5期

本文引用地址:http://www.104case.com/article/3218.htm功率MOSFET常用于便攜

和無線產品中,其應用

包括電池保護、負載管理和DC-DC轉換等。對于這些應用,功率MOSFET最重要的特性便是其漏極-源極導通電阻Rds(on)。Rds(on)較小的功率MOSFET能夠延長電池壽命,提高功率轉化效率。同時,便攜產品(如手機以及PDA等)的尺寸也在縮小,因此需要減小功率MOSFET的封裝尺寸。近年來,為同時減小Rds(on)和封裝尺寸,生產這些功率MOSFET的硅技術有了很大的改進,

功率MOSFET是典型的立式器件,漏極位于芯片的底部,源極和柵極位于上部表面。功率MOSFET經兩次擴散過程制成,先進行一次體擴散(也稱為“基極”擴散),然后進行源極擴散。為獲得大溝道寬度,功率MOSFET的設計使用了大量并行連接的單元塊。雖然每個單元的溝道寬度很小,并行連接數千個到數百萬個單元,就能得到具有極大溝道寬度的晶體管了。由于MOSFET的Rds(on)與它的溝道寬度成反比,而載流容量與溝道寬度成正比,這樣就制成了一個Rds(on)小且載流容量高的MOSFET。因此,功率MOSFET兩個重要的設計特性便是其“單元密度”(定義為單位面積中的單元個數)以及“溝道密度”(定義為MOSFET中單位面積的溝道寬度)。

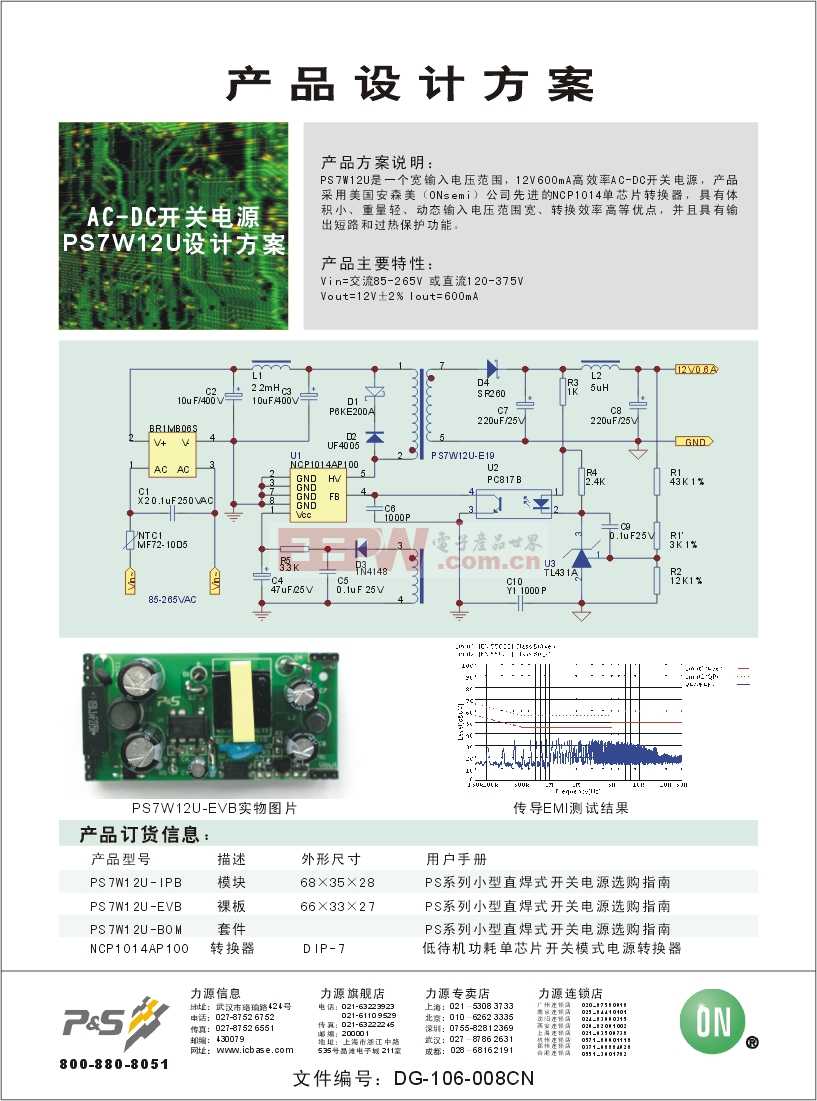

圖1所示為功率MOSFET的一種,稱為平面功率MOSFET。在平面功率MOSFET中,體擴散在公共漏極區域中形成盆狀。電流從源極流出,經過硅上部表面形成的溝道,然后垂直流過漏極,到達晶片的底部。在這種結構中,相鄰體擴散之間的間隔不能做的很小,因為這樣會導致盆之間的JFET區域被夾斷,致使Rds(on)增大。因此,平面功率MOSFET的單元密度受其溝道長度以及相鄰體擴散之間間隔的限制。直到最近,市場上大多數功率MOSFET都是平面功率MOSFET。

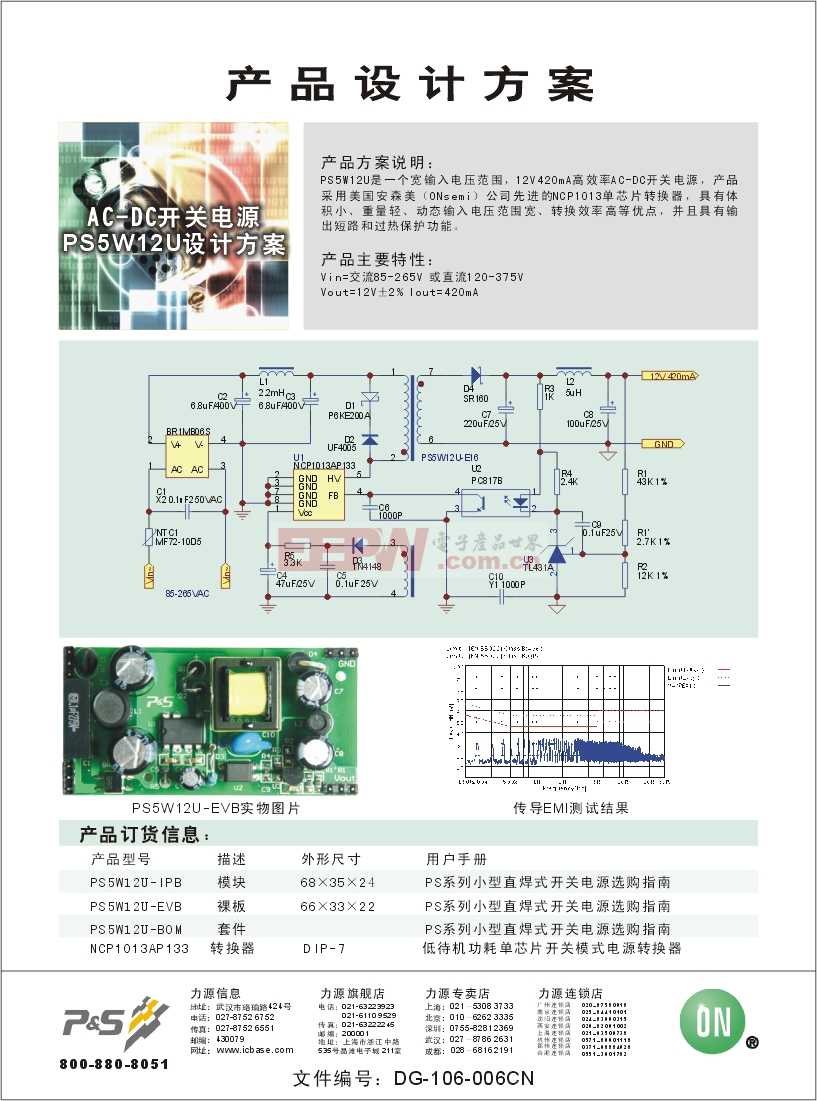

另一種類型的功率MOSFET為溝道功率MOSFET,如圖2所示,這種MOSFET近幾年已經越來越流行。與平面功率MOSFET不同,溝道MOSFET的溝道是在蝕刻于硅上的溝道邊墻上垂直形成的。溝道從硅的上部表面穿過源極和體擴散,一直延伸到漏極區域。由于溝道是垂直形成的,在體擴散之間沒有間隔限制,所以溝道MOSFET能夠達到的溝道密度比平面功率MOSFET高得多。因此,對于給定的芯片尺寸,溝道功率MOSFET能夠獲得大大小于平面功率MOSFET的Rds(on)。這改善了Rds(on)的性能,然而由于過程變得復雜,成本較之平面功率MOSFET也有所提高。

近幾年來,Rds(on)極小的溝道MOSFET已經面市,應用于諸如SO-8、TSSOP-8等的封裝中。然而,由于近來便攜和無線應用中的封裝尺寸有越來越小的趨勢,這些相對較大的封裝正被TSOP-6、ChipFET(1)及SC-88等較小的封裝所取代。由于能夠放入這些小尺寸封裝中的芯片尺寸也較小,這就增大了MOSFET的Rds(on)。因此,我們需要一種能形成較小Rds(on)的溝道技術。最近,安森美開發了一種創新的P溝道MOSFET技術,以便攜和無線產品為應用目標。

圖1 平面功率MOSFET的截面圖

圖2 溝道功率MOSFET的截面圖

器件設計

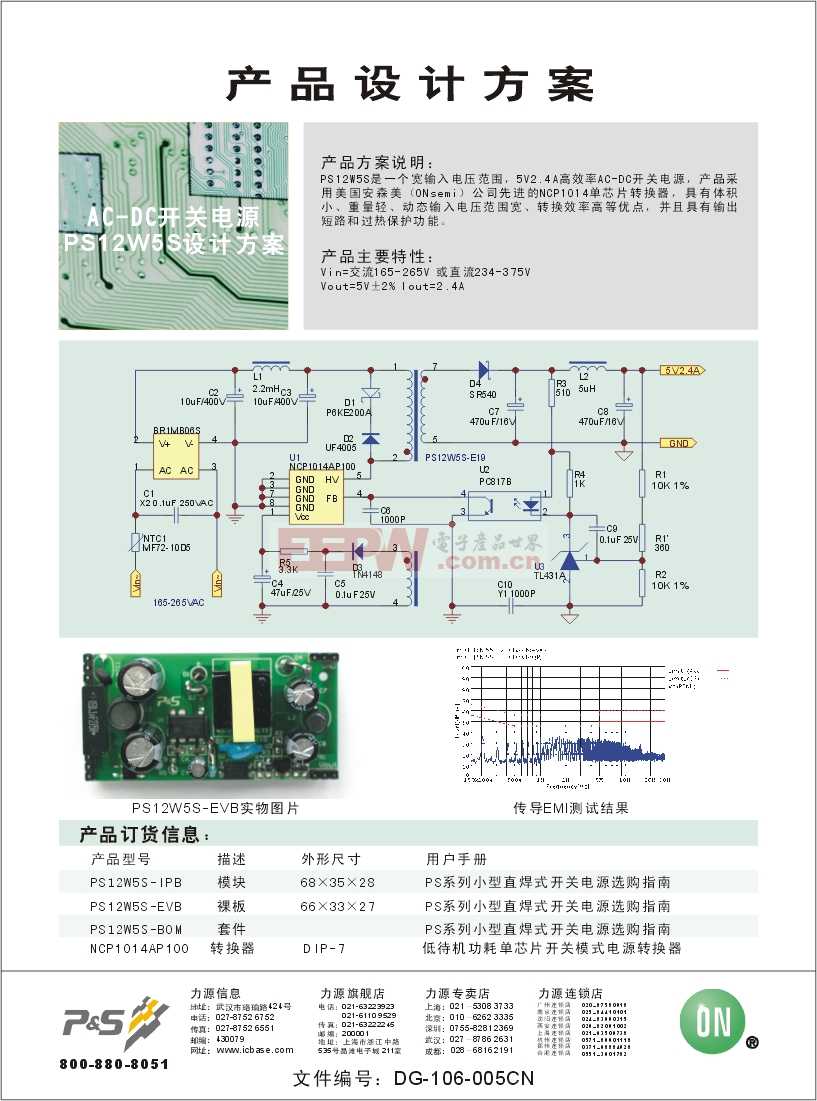

溝道功率MOSFET的設計可以使用閉合單元或條紋設計。在單元設計中,柵極在硅中形成一個柵格,包圍了體區域和源極區域;而在條紋設計中,柵極設計為條紋狀。現在市場上的溝道MOSFET使用了各種不同的布局,如方形單元、六邊形單元和條紋等。選擇哪種布局會影響溝道MOSFET的溝道密度,由此影響其Rds(on)。圖3列出了最小單元間距相同的方形單元設計和條紋設計的溝道密度對比。可以看到,只要多柵極寬度wg小于源極區域的寬度ws,單元設計的溝道密度較高,因此Rds(on)也較小。

隨著對更小的尺寸、更薄的柵極氧化物和更高的單元密度的需求不斷增加,大多數MOSFET制造商在其最新的溝道產品中都轉而使用了條紋設計。這是因為條紋設計避免了單元設計中固有的幾個角,通常使柵極氧化物的質量更優,并且易于制造。但這種條紋設計有著減小溝道密度的不利影響,因而提高了Rds(on)。安森美半導體的溝道處理技術能夠在制造中同時實現小尺寸的溝道MOSFET、薄柵極氧化物和高單元密度,在使用方形單元設計的同時保證柵極氧化物的質量和可制造性。使用方形單元設計,能夠得到1.25mm/mm2的溝道密度,比其他MOSFET制造商的溝道密度高出約40%。

器件制造

這種新型MOSFET使用0.40mm光刻法制造。P溝道MOSFET的制造從外延晶片開始,包括重摻雜P型襯底上的一層輕摻雜P型硅。應適當選擇輕摻雜P型外延層的電阻率和厚度,以獲得器件要求的擊穿電壓。接下來,使用標準的半嵌入式LOCOS工序來定義器件的有效面積區,以及端子區域的生長域氧化物。接著將磷植入有效區域并發生擴散,形成N體區域。隨后,一個用于確定溝道的硬掩模被沉積并形成圖案,接著是溝道蝕刻。然后,生成一個犧牲氧化物,并進行蝕刻。犧牲氧化物的目的是使溝道的邊角圓滑,并使硅表面因溝道蝕刻而造成的粗糙變得光滑。接著生成一層薄的柵極氧化物,再進行多晶硅柵極沉積和蝕刻。然后進行擴散工序,P+源極植入和N+體增強植入,形成與N體的連接。接點和金屬是使用傳統工序形成的。

圖3 (a)單元設計;(b)條紋設計

性能

單元和條紋設計在相同的掩模上具有不同的最小間距(即不同的單元密度)。這樣就能直接在同一晶片上比較不同的設計,消除了與工序或與初始材料相關的變化所引起的性能差異。

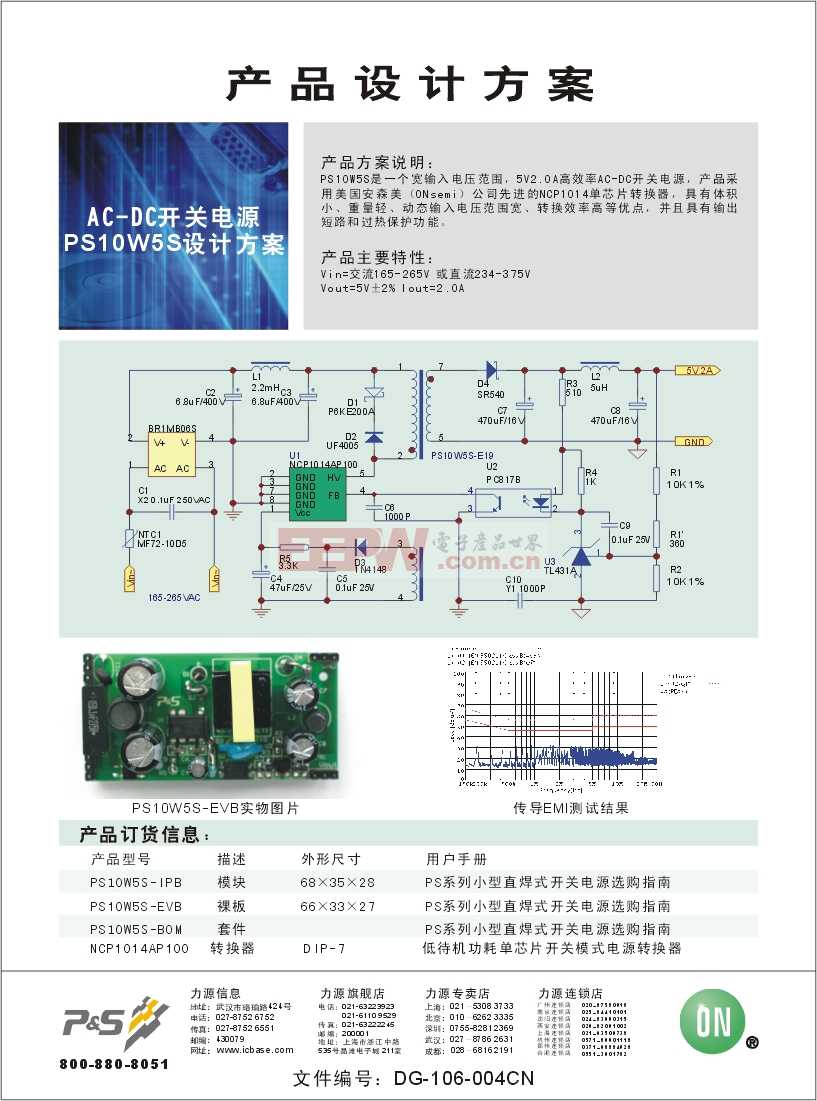

ChipFET封裝式溝道MOSFET的特性表明,在柵極電壓為4.5V的8V和20V P溝道器件中Rds(on)分別為19mW和21mW。這比原先相同封裝的Rds(on)值低了約40%。在柵極電壓較低(如2.5V和1.8V)時,也可實現類似的Rds(on)改進。

單元設計與在同一晶片上制造的條紋設計相比,柵極到源極的漏泄、漏極到源極的漏泄、擊穿電壓和閾值電壓都沒有明顯的差異。柵極擊穿試驗顯示兩種設計的柵極氧化物的擊穿場強約為10mV/cm,說明方形單元的設計并沒有影響柵極氧化物的質量。

將單元設計的Rds(on)與具有相同間距(即相同的單元密度)的條紋設計相比,發現單元設計的Rds(on)比條紋設計小。這是我們可以預料到的,因為雖然單元密度相同,但條紋設計的溝道密度比單元設計低。這表示要獲得與單元設計相同的Rds(on),條紋設計必須具有比單元設計更高的單元密度(即器件尺寸更小)。■

評論