超低功耗DDC工藝技術幫助中國IC設計業撬動IoT巨大商機

近兩年來中國IC產業勢力和相關資本的幾個大手筆收購事件以及IC Insight 最新榜單中兩家中國大陸IC設計公司闖入全球10強,讓今年的ICCAD(中國集成電路設計業2015年會暨中國集成電路產業創新發展高峰論壇)顯得格外熱鬧和引人注目。會上,中國IC設計分會理事長魏少軍公布,2015年中國IC設計產業持續擴大,銷售額將達到人民幣1234.16億元,將成長25.62%,占全球IC設計產業32.39%。據中國半導體協會統計,中國IC設計公司目前統計有736家,較去年的681家擴大了55家。

本文引用地址:http://www.104case.com/article/284842.htm中國IC設計公司成長快速的背后離不開一眾IC設計服務和代工廠的推動,本屆ICCAD可以說聚齊了中外IC設計服務和代工業的大半壁江山,重組一年多的富士通旗下半導體制造、測試服務公司——三重富士通半導體(MIE Fujitsu Semiconductor),以及整合了富士通和松下電器在圖像、網絡等應用領域LSI豐富經驗和技術優勢的索喜科技(Socionext)就攜手亮相本屆ICCAD,向新老合作伙伴展示特色超低功耗工藝和嵌入式系統代工技術優勢,以及從Turn-key的Customer SoC設計到具有成本效益的COT訂制的一站式服務。

在萬物互聯風起云涌的今天,中國IC設計公司也涌現出越來越多的玩家,進入傳感器、低功耗MCU、無線連接等芯片方案領域,以追逐移動終端應用處理器之外更加廣闊的市場空間,把握智能化和IoT大潮帶來的更大商機。因此,在IC工藝/制程方面也從一味追逐邁向摩爾定律的更深亞微米工藝節點,轉向更多討論現有技術節點功耗降低等方面的改進上。

作為業界首家且唯一一家引進超低電壓和超低漏電晶體管技術并可從事大量生產的代工企業,三重富士通半導體這次重點展示了自己開發的一系列已量產低功耗工藝技術和一項叫做“Deeply Depleted Channel(DDC)”的新工藝技術,值得廣大IoT和嵌入式應用領域IC設計公司的關注,這類工藝技術甚至可以稱得上是幫助IC設計公司撬動IoT億萬商機的“支點”。

業界唯一以DDC技術達到超低電壓和超低漏電晶體管技術的代工廠

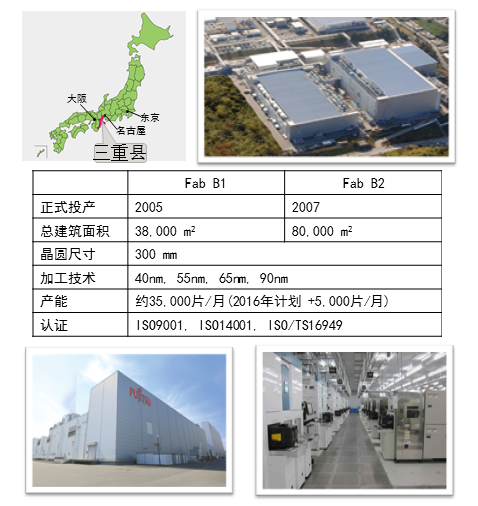

三重富士通半導體(以下簡稱MIFS)于2014 年12 月接管富士通半導體在三重工廠的300mm 生產線和配套設施,由此一個代工專業企業便應運而生。該公司將公司總部及市場營銷的據點設在日本橫濱以拓展全球性業務。

MIFS技術開發部部長倉田創在ICCAD主題演講中表示:“順應智能化及IoT為代表的新興市場的增長、擴大趨勢,MIFS憑借超低功耗制程和內存嵌入系統的優勢強項并以配備經驗豐富的工程師、不斷改良生產、混合隔震建筑等高風險應對能力為基礎,致力于發展為以降低功耗并控制成本為特色的代工企業,從而服務于物聯社會的技術革新。”

圖:三重富士通半導體技術開發部部長倉田創在ICCAD發表主題演講。

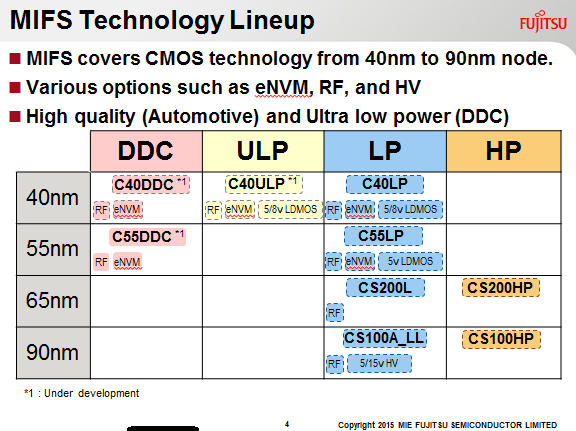

降低功耗并控制成本是IoT市場的關鍵,已成為半導體行業的最大課題之一,MIFS通過改善成本效率最為出色的平面CMOS工藝技術來解決這一問題。MIFS覆蓋了從40-90nm節點的低功耗CMOS技術,提供eNVM、RF和HV多種選項,可支持汽車應用等高品質要求的,超級低功耗應用的DDC工藝新技術是由美國SuVolta, Inc.開發,而三重富士通半導體將制程工藝技術開發完成,并開始逐步量產,DDC具有在超低電壓下可保持運作的晶體管與超低漏電晶體管技術。

獨創超低功耗工藝技術——DDC解讀

為了減少CMOS電力的功耗就有必要降低電源電壓,而長期以來的一般做法都是采用通過晶體管微型化來實現降低電源電壓。 但在90nm時代以后,由于晶體管的雜質不均引起閾值的電壓不均,從而造成即使微型化也難以降低電源電壓。

為實現移動穿戴設備等IoT應用不可或缺的低功耗應用,MIFS開發出DDC工藝技術。這項技術可以制造極低漏電型晶體管, 使其得以在極低Vdd下操作以實現最大的電源效率。將DDC與混合信號/RF及嵌入式NVM一起運用于40nm/55nm CMOS,不管對高度集成模擬還是對IoT/可穿戴式平臺的RF SoC來說都可以實現低成本、高效用。

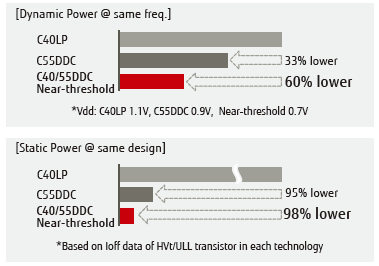

倉田創部長舉例說道:“在相同的運行速度下,55nm DDC較傳統55nm CMOS工藝降低了46%的總體功耗,較傳統40nm工藝降低了18%。此外,超低漏電晶體管也將泄漏電流從皮安培(pA)降低到毫微微安培(fA)。”

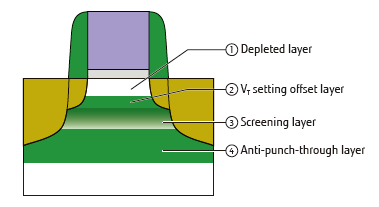

圖:DDC構造。

DDC是Si基底的耗盡型溝道器件,通過簡單的bulk planar工藝(平面加工工藝)制成。晶體管的通道部分由于形成多重不同濃度的雜質層,減少雜質波動這一造成閾值電壓(Vth)不均的重要因素的影響,從而達到降低電源電壓的目的。因采用傳統的平面CMOS結構,不僅可以使用于現有的生產線裝置,同時在電路設計方面也可以靈活運用現有的裝置是其一大優勢。

倉田創部長將DDC的主要優點歸納為以下三點:

1) 電源消耗極低:采用DDC以及降低操作電壓可以實現電源總消耗的大幅度減少。

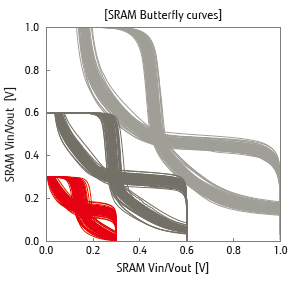

2) 降低SRAM的Vddmin:如果降低Vdd的同時增加Vt的話,SRAM的電池操作一般會變得不穩定。DDC可以實現在Vdd極低的條件下運作SRAM。即便是在Vdd=0.3V的情況下,基于DDC的SRAM蝴蝶曲線依然展現出明顯的兩扇窗口的模樣。

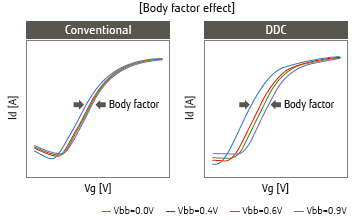

3) 強大基體因子(Body Factor)效應:DDC晶體管的body bias(Vbb)系數要強于傳統的晶體管。因此,DDC可以實現Vt的靈活控制。

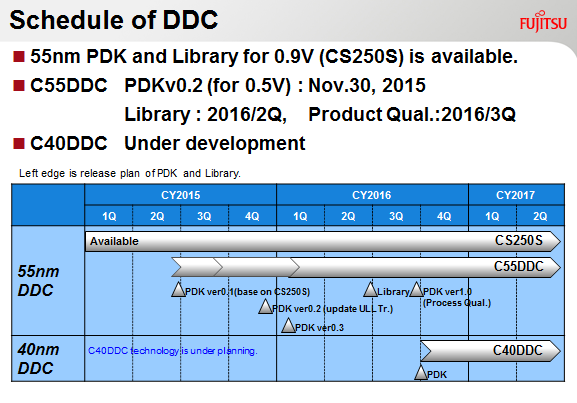

下圖是三重富士通的DDC工藝發展路線圖,2015年11月底該公司已開始提供PDK的“C55DDC”還可為客戶量身打造提供低功耗方案,包括提供靈活的工藝優化、參數調整等服務。并且,如果客戶的產品已經在別的foundry運行過,也可以到三重富士通的工廠生產,其技術人員會幫助調整參數,減少客戶開發難度。

申請體驗Shuttle service,降低流片成本

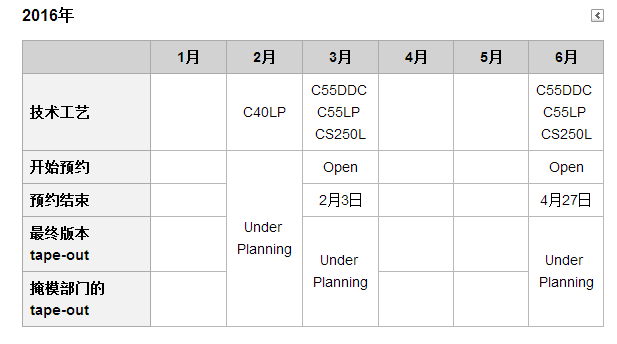

"Shuttle service"是指用降低芯片成本來驗證客戶設計的手段, 采用多項設計共享晶圓、掩模以控制成本。以下是三重富士通半導體的2016年 “Shuttle service”排期表,包括最新的55ns DDC(C55DDC)工藝技術和服務體驗也將于2016的3月、6月開放,感興趣者可提前在其官網申請。

評論